“线程”中讨论的其它部件: LM4051, TEST, TINA-TI

您好,

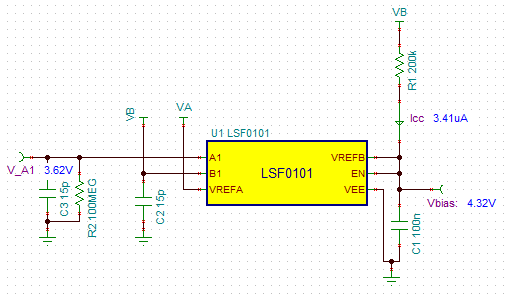

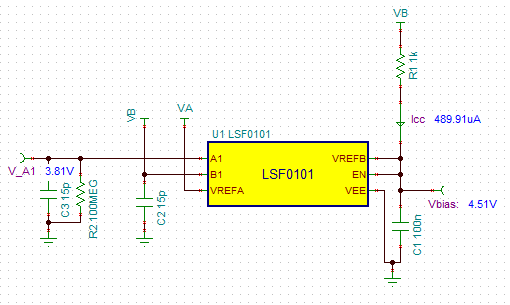

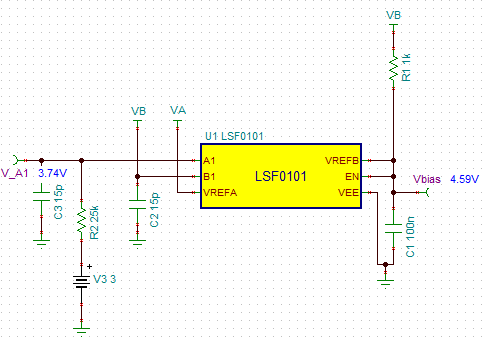

随附原理图。

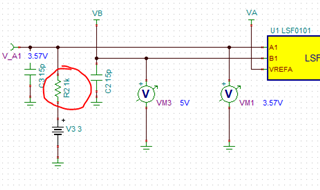

我们将 VrefA 设置为约3.6V,VrefB 设置为5V。 我们在这些电压下测量“实心”导轨。

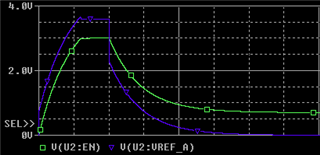

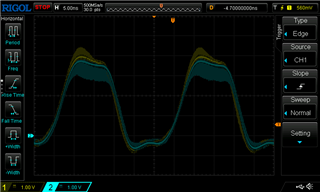

但是,LSF0108芯片(引脚19和20)的 VrefB 和 EN 在进行数据传输时,由200K/0.1uFD 网络“驱动”的电压“下降”到较低的电压......低至约2V。 由于没有数据传输,我们看到的电压大约为4.5V (即,比5V 参考电压低500mV)。 这会导致错误的 PCI 传输。

以某种方式,转移活动正在“传递”到 LSF0108芯片的 Vreb/EN 输入。

我们能否将20万美元的成本降低到相当小的程度? LM4051ADJ 断路器应该能够通过参考 FET“吸收”任何所需的电流。

此电路的目的是将5V PCI 传输(VIO = 5V)限制为3.6V,以免漏掉位于另一页的 FPGA。 FPGA 处理 PCI 传输。

我们喜欢系列 FET 样式级转换器,因为它们基本上是零延迟设备。

我们喜欢 LSF0108,因为它具有内部 FET“校准参考”,可根据3.6V VrefA 建立精确的“阈值电压”。 换言之,FPGA 的电压不应大于3.6V,这对 FPGA 来说是正常的。

但是,我们不理解为什么芯片的 VrefB/EN (引脚19和20)在数据传输过程中不稳定!

RSVP 提供建议。 您可能需要让芯片设计人员参与解释。 我们回顾了您关于“LSF”家族运营的精彩视频,但这并不能说明我们为什么要看到我们所看到的!!

谢谢你,

Joe Norrise2e.ti.com/.../schema_5F00_lsf0108.pdfe2e.ti.com/.../lsf0108.pdf