请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

您好,

请考虑响铃问题已关闭;当我们要执行EFT突发测试时,我们在缓冲区上遇到了严重的阻塞问题。

我们正在帮助解决以下问题:

以*nCS0信号(芯片选择)为焦点,在正常操作中,BP_A_nCS0由CPU切换,输出电平为0V或3.3V (如预期)。

当我们注入脉冲时,我们看到 在某些情况下,BP_a_nCS0不是处于3.3V的默认状态,而是在1.5V左右,并且保持在该水平;缓冲器似乎工作正常,因为如果CPU切换信号,我可以看到输出从0V切换至1.5V

在这种情况下:

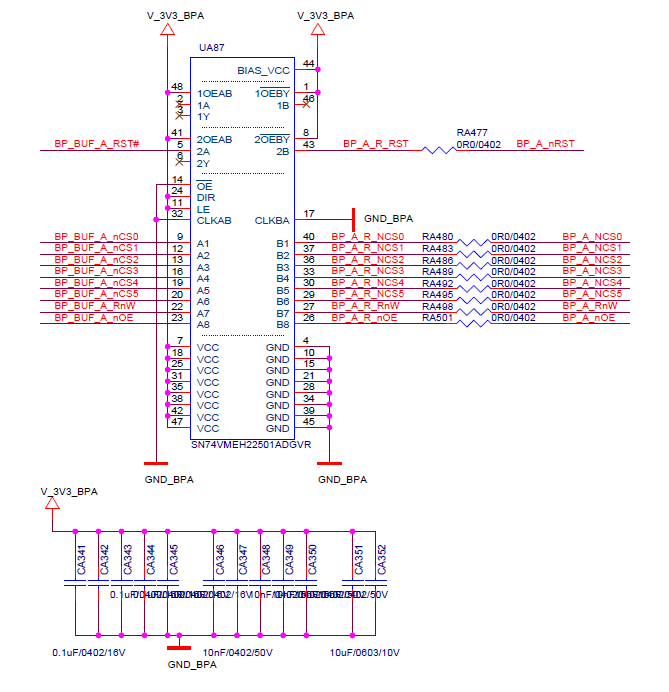

0)检查中的VME缓冲器放置在CPU板上,用于管理具有多个I/O板功能的背板架构;每个CS均可访问每个I/O板

1)未安装任何I/O板(即:拔下I/O板,因此CS信号无负载,终端除外)

2)缓冲区很热,因此似乎发生了冲突;由于不存在I/O板,因此没有任何对等点强制CS,预期缓冲区本身,因此我认为冲突是在IC内部发生的

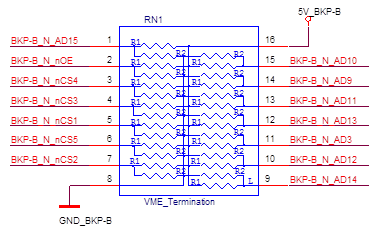

3)参见下面所附的缓冲器示意图和使用的端接(2个端接,远离并靠近CPU,每个端接具有330R/470R分压器)

请帮助我们了解在EFT突发下缓冲区为何停止工作

非常感谢