请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/581427/txb0304-about-txb0304-application

部件号:TXB0304尊敬的支持团队:

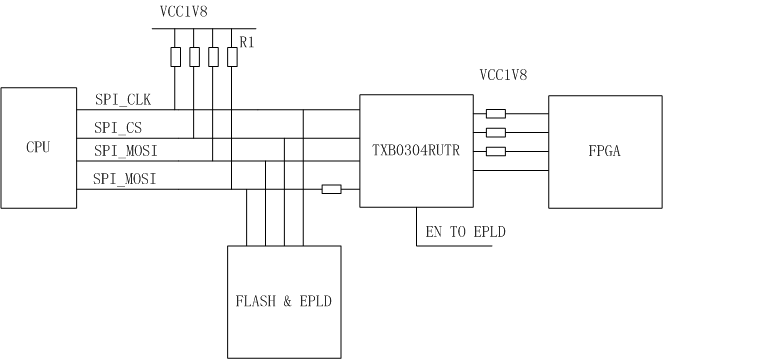

客户在下面使用TXB0304,他们使用它来隔离与具有使能功能的FPGA的连接,以避免FPGA无法通电时,FPGA会拉动SPI总线。根据我们的D/s,两侧都是1.8V电平,

1.输出不能上拉,因此它们只在输入处使用上拉, R1要高于20k,其它的使用4.7K

2.打开OneShot时,MOS内部电阻几乎为0,它们会在TX侧添加串行电阻。

您能否帮助检查设计是否正常? 太棒了!