请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

部件号:SN74AUP1G74 支持路径:/Product/开发和故障排除/

您好,

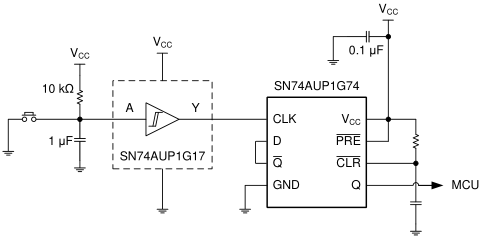

我想在我的应用程序中使用SN74AUP1G74 D-FF。

如第16页DS中所述,可通过电阻器和电容器将CLR_NOT引脚连接到Vcc。

我对这种连接有一些顾虑,因为DS没有为电阻器和电容器提供任何指导或特定值,因为这是一个到数字引脚的模拟连接。

DS中提到引脚的电压上升率必须小于200nS/V

我想知道这种连接是否被接受,电阻器和电容器的推荐值是多少。

谢谢你。