https://e2e.ti.com/support/logic-group/logic/f/logic-forum/591106/sn74lvc1g17-sn74lvc1g17

部件号:SN74LVC1G17您好,

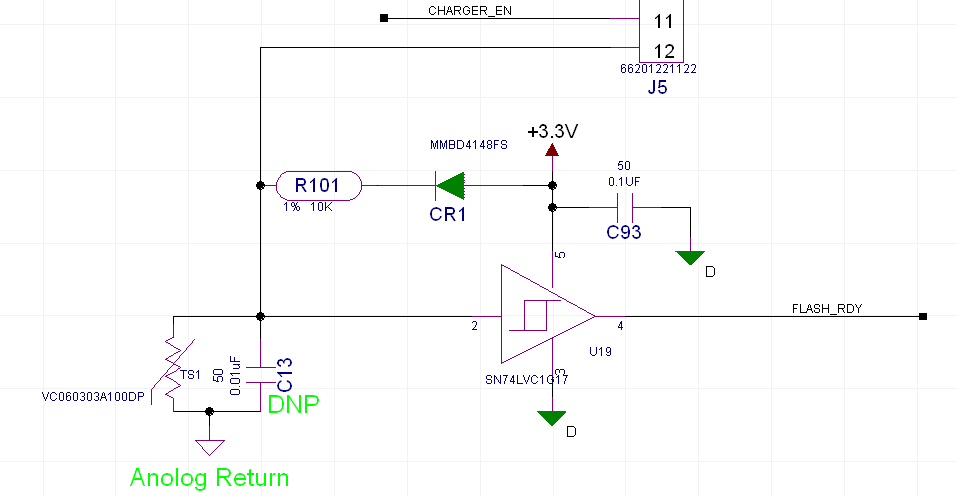

我们正在使用SN74LVC1G17来保护一个越过主板的信号。 我们知道,由于源信号上的噪音,信号有一些峰值。 源输出是闪存板上的开路漏极信号。 原理图如下所示。

Analog GND和DGND在板上有单点连接。 TS1开始夹紧5V电压,并夹紧12V电压。

最近,U19的输入(PIN2)持续燃烧。燃烧时,从PIN2到引脚3的电阻约为30欧姆。 我们检查了输入。 当闪存被触发时,来自闪存板的源信号在大约+/-120V的电压下会出现约5us至10us的峰值。 频率约为3MHz至5MHz。 噪声与输入相结合,但却没有太多能量。 该芯片专为ESD保护而设计,应该能够处理峰值。 我在擦头,什么可能导致故障?

欢迎提出任何建议。

谢谢

彭