主题中讨论的其它部件: SN74LVC541A

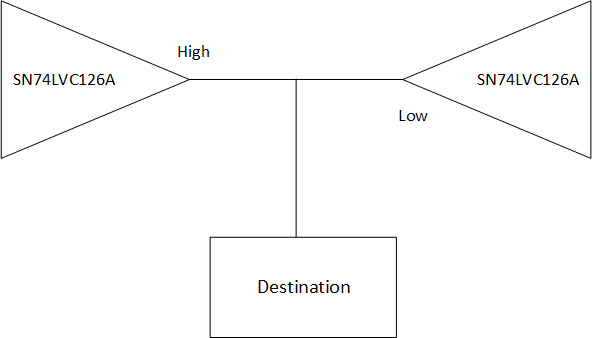

在我的应用中,有一种情况是,两个SN74LVC126A的输出 直接连接在一起,以驱动一个通用目标。 不允许串行阻尼电阻器位于之间,因为应用对串行R值敏感。

在正常操作期间,只有一个缓冲区主动驱动输出,而另一个缓冲区是三态的。

我的问题是故障模式分析-如果一个SN74LVC126A在同一根导线上以较低的速度行驶,那么芯片的潜在损坏是什么?

通常,我看到其他接线柱询问将输出短路到GND的故障模式。 我想知道 是否与我的案例中的不同之处在于,电流流经对等驱动器,而不是流向GND。 对等设备上的当前夹紧功能是否能帮助我们防止芯片损坏?

感谢您的支持。