大家好、

我们有一个有关 ESD 测试中 D 型触发器/CLK 问题的问题需要您的支持。

SN74LVC1G74在系统中使用、我们发现在执行 ESD 测试时/CLK 会受到影响并变为低电平、这会导致输出错误信号。

我们是否有解决此问题的解决方案?

如果另一个合适的器件可以解决此问题、您可以推荐它。 据我所知、可能会增加响应的延迟时间/CLK 可以解决此问题、请提供您的命令。 谢谢!

BR、

Darren

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

我们有一个有关 ESD 测试中 D 型触发器/CLK 问题的问题需要您的支持。

SN74LVC1G74在系统中使用、我们发现在执行 ESD 测试时/CLK 会受到影响并变为低电平、这会导致输出错误信号。

我们是否有解决此问题的解决方案?

如果另一个合适的器件可以解决此问题、您可以推荐它。 据我所知、可能会增加响应的延迟时间/CLK 可以解决此问题、请提供您的命令。 谢谢!

BR、

Darren

大家好、Clemens、

我的错误是、所述的/CLK 应为/CLR、清除输入功能并置为低电平以设置输出低电平。 在 ESD 测试中、我们发现 /CLR 可能会受到影响并变为低电平。

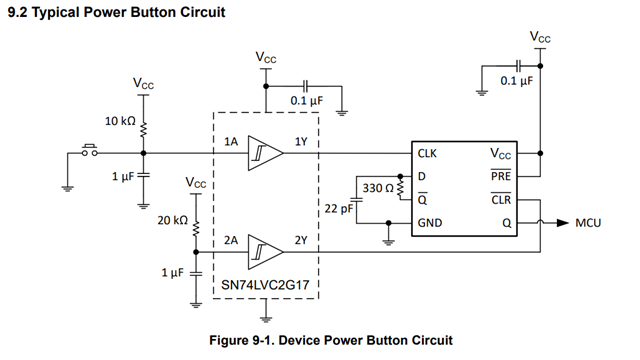

1.您能否分享如何在电路中添加低通滤波器解决方案? 下面是典型电路。

2.是否有另一个器件对 /CLR 变化具有低压摆响应或延迟时间? 也许这是另一个想法、您能分享您的评论吗?

BR、

Darren