主题中讨论的其他器件:SN74LVC1G17、 SN74HCS74

此应用是电源开/关按钮控制。

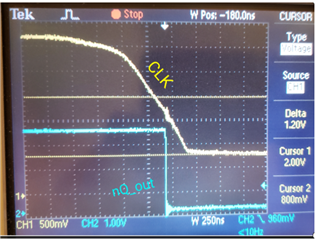

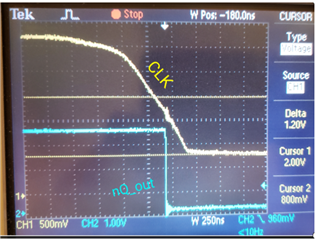

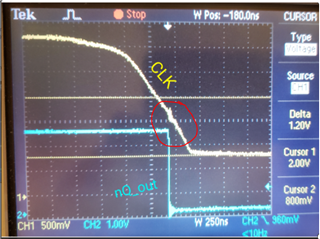

CLK 输入上有 R-C 延迟电路、这使得时钟的上升沿和下降沿慢于数据表中建议的最大值(3.3V 时) 10ns。

虽然 触发器在缓慢上升的 CLK 边沿上工作正常、但当 CLK 以几乎相同的500ns/V 低速率下降时、它也会改变其状态

是否需要此行为?

如果比较器放置在 CLK 前面以校正慢速下降时间沿、它是否会修复意外的触发器变化状态?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

此应用是电源开/关按钮控制。

CLK 输入上有 R-C 延迟电路、这使得时钟的上升沿和下降沿慢于数据表中建议的最大值(3.3V 时) 10ns。

虽然 触发器在缓慢上升的 CLK 边沿上工作正常、但当 CLK 以几乎相同的500ns/V 低速率下降时、它也会改变其状态

是否需要此行为?

如果比较器放置在 CLK 前面以校正慢速下降时间沿、它是否会修复意外的触发器变化状态?

您好、Boris、

CLK 输入上是否需要 RC 电路?

是的、由于您违反了输入转换速率要求、因此会出现预期行为。 时钟信号的下降沿有一些噪声导致器件触发。 请参阅此常见问题解答 慢速或浮点输入如何影响 CMOS 器件? 以了解更多详细信息。

如果 比较器具有足够快的开关时间来满足输入转换速率要求、则可以放置一个比较器来校正慢速下降沿时间。

此致、

Sebastian