请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC2G17 大家好、e2e 团队、

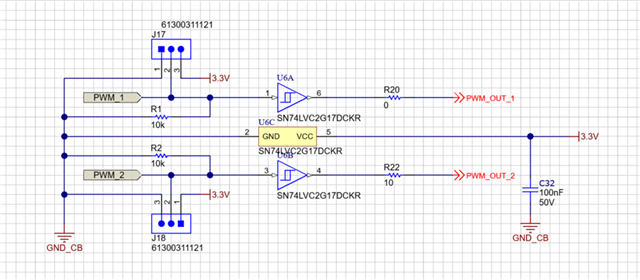

我在设计中使用的是 SN74LVC2G17缓冲器、通过下拉电阻器10k Ω-->按如下方式连接了 PWM 输入

问题是当我提供3.3V 电源时、引脚2 (J17和 J18的引脚2)都被上拉(~2.3V)、而不是通过下拉电阻器由 GND 连接。 我看到 PWM 输入波从2.3V 变为3.3V、而不是从0变为3.3V ->电平位移。

请告诉我这里可能是什么错误来源? 我甚至尝试用1k 和100k 替换10K 电阻器值、但仍然没有变化。

谢谢、

Anubha