Other Parts Discussed in Thread: SN74LVC162244A, SN74LVC2G125

主题中讨论的其他器件:SN74LVC162244A、

您好!

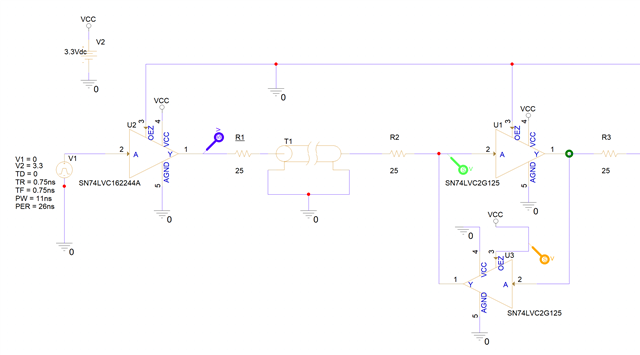

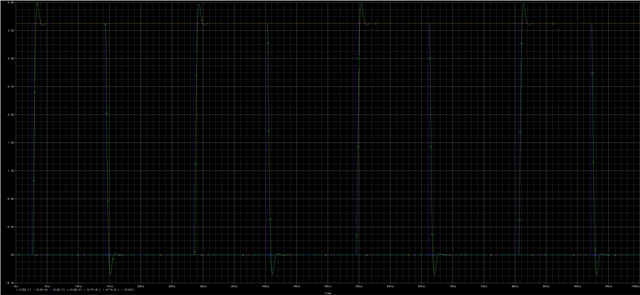

我设计了一个采用 SN74LVC2G125和 SN74LVC162244A 的电路、如下图所示。 在我的仿真结果(如下图所示)中、我期望 U1引脚2的电压(绿色波形)是 U2引脚1的电压的延迟副本(蓝色波形)。 但是、会发生的情况是、U1引脚2上的电压接近于0V、并在 U2尝试将其电压驱动到 U1时产生一些振铃。

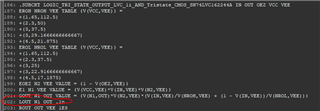

我的假设是 U3的输出使能不能正常工作、因此 U3不处于高阻抗状态、并以某种方式干扰 U1的输入。 我怀疑这是因为当我将 U3的 VCC 接地并重新运行仿真时、我会得到下面第三张图片中显示的结果、其中 U1引脚2的电压现在跟随 U2引脚1的电压、并具有一些过冲/下冲和延迟。

现在、我的问题是:如果器件型号的数据表给出了这样的说明、为什么不能将 U3的输出使能端提高到 VCC 以将其置于高阻抗状态? 我们为什么还需要将其 VCC 引脚接地?

谢谢你。