您好!

我尝试使用 IBIS 模型将 LSF0101器件中的延迟与数据表中的设置相关联。 我对此有2个问题。 我看到的结果与数据表中的结果不完全相同。

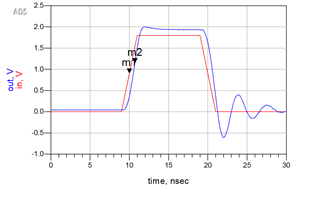

输出到输入延迟为~0.7ns。 列出了1ns

2.在测试设置中,OUT 信号不会达到3.3。

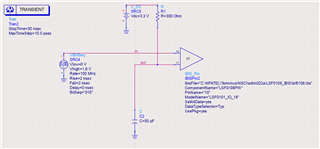

下面是 ADS 设置的快照。 您能否看到是否需要更改任何内容以与数据表结果相关联。

谢谢。

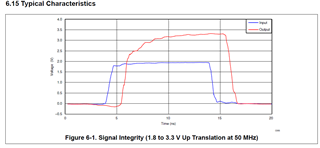

数据表输出

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、Nikhil、

我不确定 我是否理解您的担忧、因为0.7ns 应优于1ns (相差仅0.3ns)。 但是 、请注意、IBIS 模型并不是为了验证延迟、因为它们主要用于信号完整性。

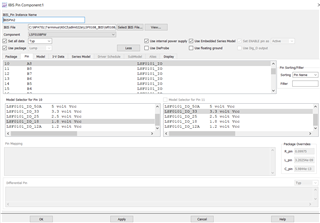

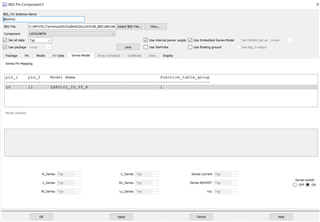

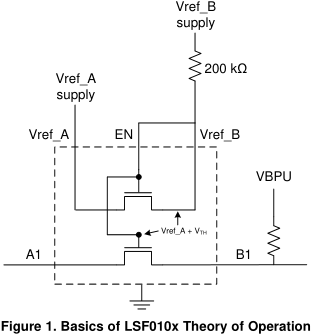

该器 件也是无源开关;通过将 VrefA/VrefB 引脚直接连接到内部 FET 的源极/漏极(如下所示)、无需使用 IBIS 对任何缓冲 I/O 建模、IBIS 模型的运行方式与模拟行为类似、就像开关一样。 因此、该模型无法将1.8V 输入转换为3.3V 输出、例如、它只能进行相同的电压转换。 (请参阅 [常见问题解答]如何估算模拟开关/多路复用器中的传播延迟和通道间偏移?)。

您的情况也不可能与 您提供的数据表输出类似(在理想情况下)的测试条件匹配、这会使系统发生变化、并进一步建议使用 LSF EVM 来测试和验证信号完整性以及延迟。 另请参阅 [常见问题解答] LSF 转换器如何工作?、谢谢。

此致、

Michael。