请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVCH16T245 主题中讨论的其他器件:SN74AHCT16541

我们使用的是 SN74LVCH16T245。

A 侧连接电源+3.3V,并连接 FPGA 输出(LVCMOS3.3V)。

B 侧连接电源+5V,连接 ULN2803ADWR 的输入。

方向为→B

所有 OES 均为 GND。 所有 DIR 均为+3.3V 连接。

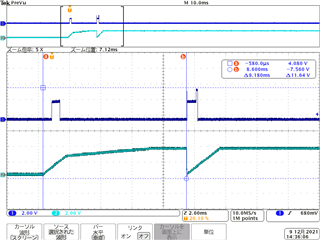

随附的图片显示了 SN74LVCH16T245 B 侧(8引脚)的波形在顶部、而+3.3V 电源的上升波形在底部。

不清楚输出上的波形在大约2V 的信号中、这可能是因为方向从 B 变为 A 直到+3.3V 上升。

此外、+5V 启动的电压比+3.3V 低。

FPGA 信号很可能处于开路状态。

请告诉我这种现象的原因。

请告诉我原因和对策。