主题中讨论的其他器件:SN74AUC2G126、 SN74AUC1G126

当 VDD = 1.8V±5%时、该器件是否支持66.66MHz 输入方波?

在本例中、CL = 15pF 时预期的 TR/TF 是多少?

是否观察到该器件用于缓冲时钟信号的应用?

(我担心抖动和时钟信号衰减...)

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

当 VDD = 1.8V±5%时、该器件是否支持66.66MHz 输入方波?

在本例中、CL = 15pF 时预期的 TR/TF 是多少?

是否观察到该器件用于缓冲时钟信号的应用?

(我担心抖动和时钟信号衰减...)

在1.8V 时、LVS 可以实现80MHz 的频率。

在1.8V 电压下、诸如 SN74AUC2G126的 AUC 系列器件的工作电压大大好于 LVC。 (请注意、AUC 输出在转换期间会改变阻抗、因此无法像常见问题解答中一样轻松估算上升/下降时间;请参阅 AUC 应用报告。)

尊敬的 Emrys:

我仍然需要知道输出的预期上升/下降时间。 对于以下情况、我们是否有任何数据?

如果可能、我需要最大值/最小值。

- VCC:1.8V 或3.3V

- TR/TF 范围:20%~80% VCC

TR/TF 范围:35%~65% VCC

CL:15pF

我希望输出 TR/TF 独立于输入 TR/TF、是吗?

(逻辑缓冲器不是放大器;当输入超过特定阈值时会触发输出)

此致、

Darren

尊敬的 Emrys:

我阅读了您的博客文章并进行了一些数学计算。

我认为我对这个过程有了很好的理解(t =-rrrC*ln (1 - dV))

您能否检查我的数学运算(Excel)

3.3V 时、LVC 的功耗小于200ns、1.8V 时、AUC 的功耗小于~300ns。

(CL = 15pF、35%~65%Vcc = DV = 0.3)这些数字使用 MAX RDS (on)、所以实际上属于最坏情况?

AUC 逻辑缓冲器 SN74AUC1G126是否能够处理125MHz 输入/输出?

这是一个4ns/4ns H/L 信号、我对1.4ns 最大 tpd 有一点紧张。

您会推荐2.5V/125MHz 的逻辑器件吗?

此致、

Darren

您好 Darren、

在典型负载下、AUC 器件的上升时间将低于1ns。 这些是逻辑产品系列中最快的器件。

[报价 userid="403768" URL"~/support/logic-group/logic/f/logic-forum/1132182/sn74lvc2g126-output-rise-fall-times/4205192 #4205192"]我们是否有以下条件的任何数据?不、恐怕不是。 上升和下降时间不是器件规格或特性的一部分--如果是,它们将在数据表中。

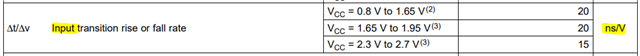

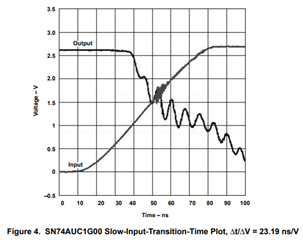

[引用 userid="403768" URL"~/support/logic-group/logic/f/logic-forum/1132182/sn74lvc2g126-output-rise-fall-times/4205192 #4205192]I 希望输出 TR/TF 独立于输入 TR/TF、是吗?是的、这是正确的、但是慢速输入会导致不稳定的行为、这将影响输出信号。 所有 CMOS 输入都需要满足数据表要求:

应用报告《 德州仪器 AUC 低于1V 小尺寸逻辑器件的应用》

我认为你的成绩是1000倍(我没有检查你的 Excel)。 对于10%至90%、您可以使用简单的公式:T_t = 2.2 * R * C

当 CL = 15pF 且使用 LVC 器件(约13欧姆)时、上升时间计算为 约195ps。

正如 Clemens 提到的、AUC 器件具有可变的输出阻抗、因此这种类型的计算方式无法很好地与之配合使用。

-

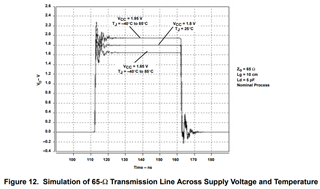

从我先前链接的同一应用报告中、有一个用于驱动来自1.8V AUC 系列器件的传输线路的波形:

您可以看到、边沿速度极快。 AUC 系列可轻松驱动125MHz 信号。

大家好、Clemens、

我感谢各位的评论。 我们关心 TR/TF、因为对接收器件有非常严格的要求。

(即15pF 负载的最长上升时间为513ps、从信号幅值的35%~65%测得)

尊敬的 Emrys:

你是对的、我想说[ps]而不是[ns]。

随附的该文档的图13使您更容易看到5pF 的典型 TR/TF。

绝对低于1ns

最后一个问题:

我注意到数据表将"tpd"指定为独立值。

这是否意味着 H-L 转换的 tpd 和 L-H 转换完全相同?

如果存在偏移、该怎么办? 此信息对于了解在较高频率下预期的占空比降级程度非常重要。

此致、

Darren

不可以、这只是意味着两个值中较大的值不会超过数据表中提供的限制。 T_PD 是 t_plh 和 t_PHL 较大者的速记。

未指定偏差。

我建议他们查看 TI 的时钟缓冲器产品系列、因为这些产品将指定抖动和偏斜、并且具有出色的性能。