Other Parts Discussed in Thread: SN74LVC3G17, TLV741P, TLV713P, SN74LVC541A, LM5114, SN74HC14, SN74AHC14, SN74HCS14, SN74LV1T34

你(们)好

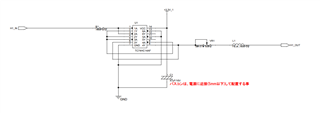

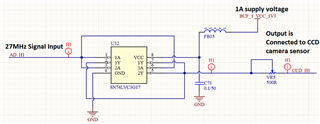

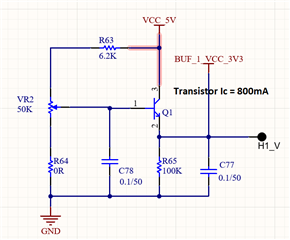

我们将 SN74LVC3G17用作系统中的缓冲器。

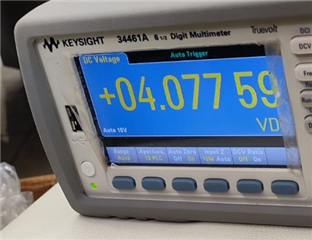

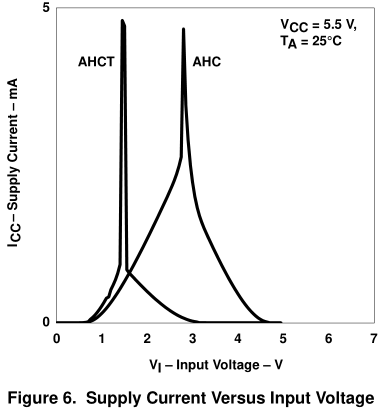

在为缓冲器提供输入信号(24MHz)的同时、缓冲器 VCC_3V3的电压会下降、大约为300mV。

尽管我们为缓冲器提供了大约1A 的电源电流。

我们仍然感到困惑的是、为什么即使缓冲器由足够的电源供电、缓冲器的 VCC 电压也会下降。

请您检查一下、我们已附上一个片段供您参考。

\

\