Other Parts Discussed in Thread: SN74LVC2T45, SN65LVDS31, SN65LVDS33, SN74LVC2G04, SN74LVC1G79, SN74AUC1G04, SN74HCS74

https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1057646/sn74lvc2t45-frequency-calculation

器件型号:SN74LVC2T45主题中讨论的其他器件: SN65LVDS31、 SN65LVDS33、 SN74LVC2G04、 SN74LVC1G79、 SN74AUC1G04、 SN74HCS74

早上好、

我对计算 非时钟器件的最大工作频率有疑问。

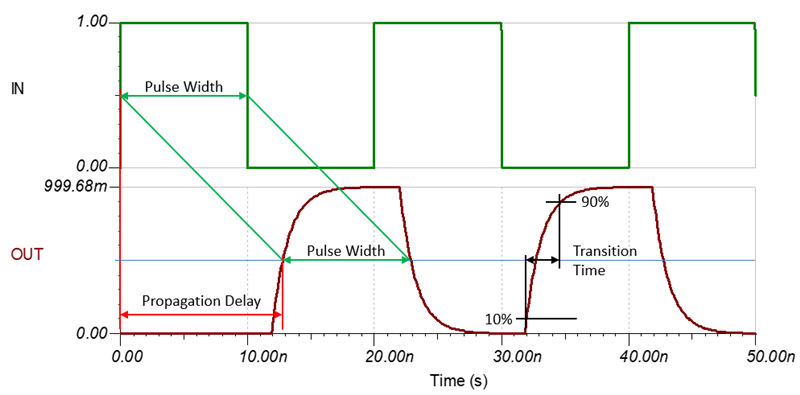

TI 的经验法则是、2 x tpd 的倒数或 tPLH + tPHL 的倒数定义了最大工作频率。

我如何看到传播延迟-> 移动由 tPLH 上升的输入信号、并移动由 tPHL 下降的信号。

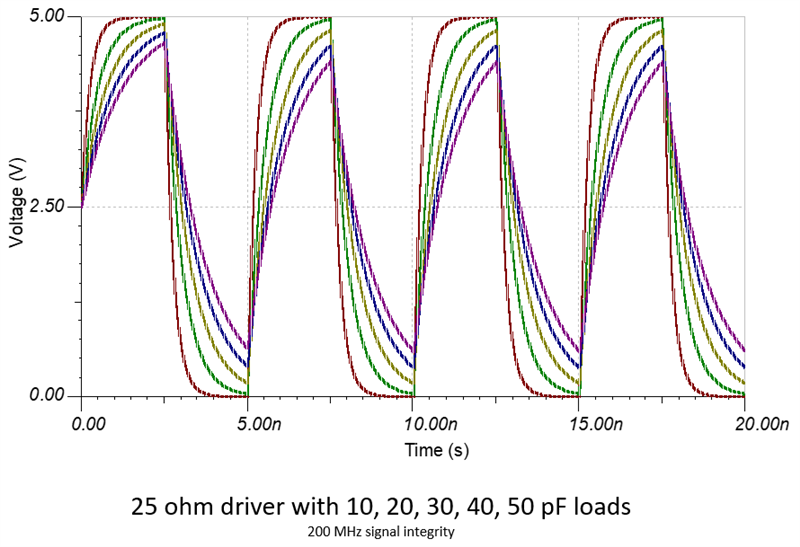

我还认为上升时间和下降时间也会影响工作频率。 我有几个问题要问您、以帮助我了解工作频率计算以及我希望 使用特定输入将 SN74LVC2T45输出的结果。

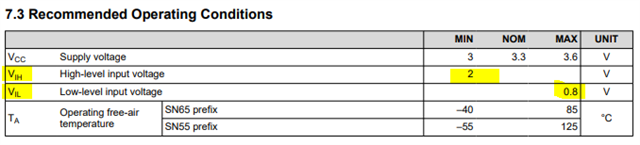

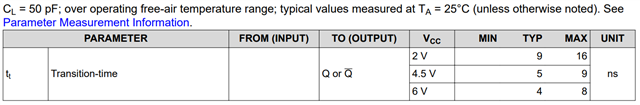

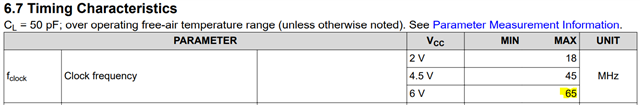

1)在我的应用中、 Vcca 为3V3、Vccb 为5V。 对于这些电压电平、最大 tPLH->4.4ns、最大 tPHL 为4ns。 TPLH + tPHL -> 8.4ns。 因此、该 IC 的最大工作频率为119MHz。

如果我有一个80MHz 的时钟作为一个上升和下降时间为1ns (20-80%)的输入、我该怎么办? 当我检查电平转换 器 DT/DV 数据表时、当 VCCI 为3.3V 时、输入转换上升或下降速率被指定为最大值10ns/V。

您能否给 该电平转换器抽取一个上升时间为1ns (20-80%)的80MHz 输入时钟、以及我希望将什么作为输出?

当我查看数据表第12页-> VCC1/2时、VCCO/2出现在输出端。 我不理解在3V3电平信号的33ns 上升时间下这是怎么可能的?

您认为您可以在这里帮助我理解整个概念吗?

此致

Onur