Other Parts Discussed in Thread: SN74LVC4245A, SN74LXC8T245

主题中讨论的其他器件: SN74LXC8T245

我们使用 SN74LVC4245A 来控制5V 输出逻辑信号、并且在上电期间发现了一个问题。

该组件配置为将3.3V 逻辑信号从其 B 侧(VCCB=3.3V)移动到 A 侧(VCCA=5V)。 DIR 引脚设置为 GND、OE 引脚通过4.7K 电阻连接到5V (如数据表中所建议)。 稳压器从5V 提供3.3V 电压。 10k 电阻器下拉 COMP 的所有输出(A 侧)。

- 加电时、5V 首先斜升、因此 OE 引脚也斜升。

- 其次、3.3V 在几毫秒后开始。

- 最后、一个集电极开路晶体管将 OE 引脚置为低电平。

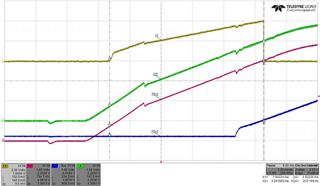

这种配置在许多情况下都能正常工作。 不过、我们发现了一个问题、即在上电之前3.3V 电源轨上仍然存在残留的0.3V 电压(由于快速断电和上电序列)。 在这种情况下、尽管 OE 引脚上有上拉电阻、A 侧输出都被错误地激活并以5V 斜升、直到3.3V 开始斜升。

遗憾的是,此问题会对输出造成有害的“闪存”行为,在上电时必须保持低电平。

例如、请参阅下面的激活 A7。

您能否说明尽管 OE 引脚处于状态、仍激活此输出的原因?

您是否可以建议进行修改以解决此问题?

谢谢