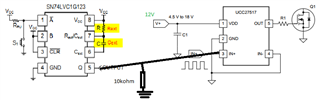

主题中讨论的其他器件: CD40109B、 UCC27517

您好!

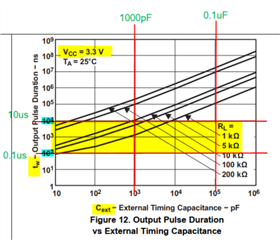

我需要生成的脉冲持续时间为0.1us 至10us。

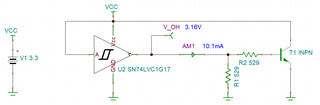

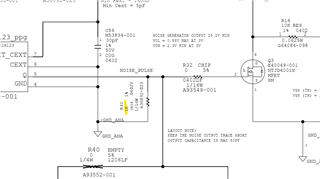

如果将1000pF 用作 Cext ,并且从数据表中的图12中可以看出 RL 为1k Ω 至10k Ω。 如果使用3.3V 电源、则 k 为1.11 (从图4.2中)

问题:

- 在本例中、Rext used 是什么? TW = K x Rext X Cext = 1.11 x Rext x 1000pF

它是否直接计算 Rext = Tw /(K x Cext)?

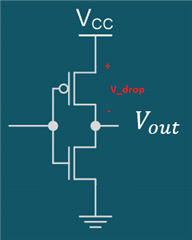

- 在这种情况下,RL 计算是如何涉及的? Rext 和 RL 都需要参与此计算吗?