请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G08 团队、

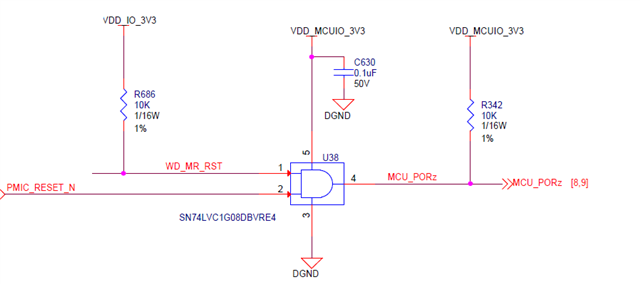

我们将 SN74LVC1G08DBVRE4用于我们的应用之一。 下图用于参考电路

引脚1 -上拉-将始终为高电平

引脚2 -在基准脉冲经过一定的延迟(12ms)后将为高电平

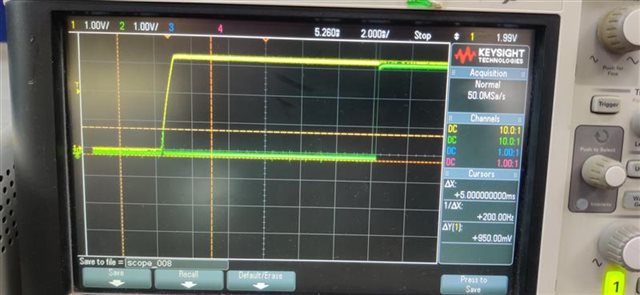

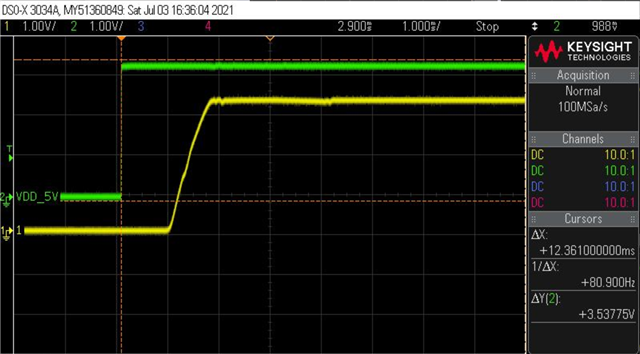

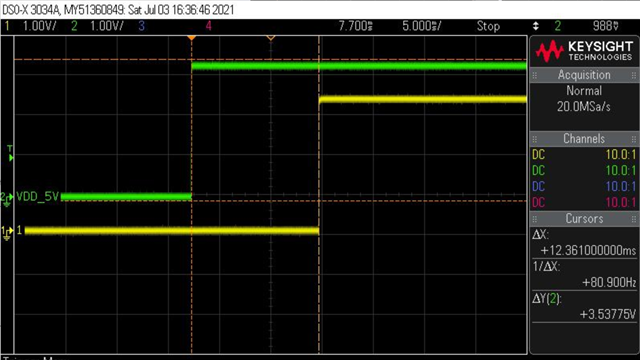

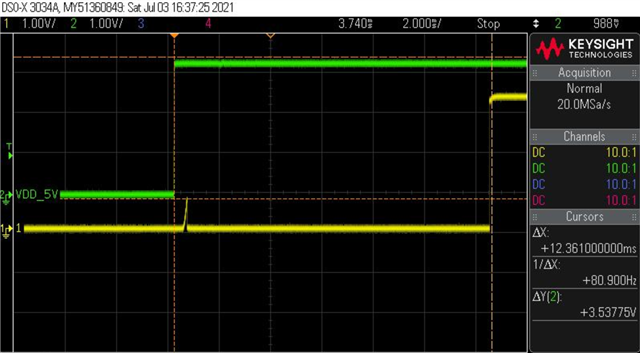

我们在与门的引脚4处看到干扰、如下图所示 、其中在输入端未看到这种干扰。 绿色波形是我们的参考波形。

图1 -针脚1 (黄色)

图2 -针脚2 (黄色)

图 3 -引脚4 (输出) (黄色)

请您在这方面提供帮助。

BR、

Arun