主题中讨论的其他器件:SN74AUC1G125、

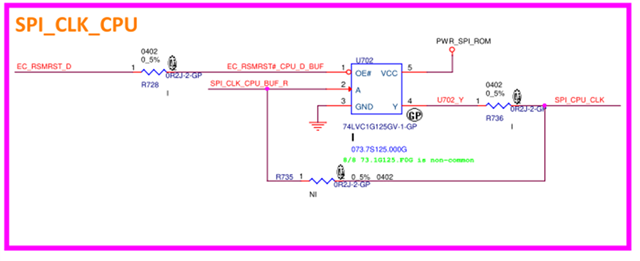

大家好、

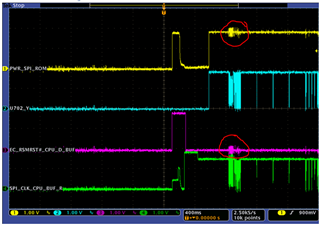

我的客户发现在使用缓冲器时没有时钟信号、

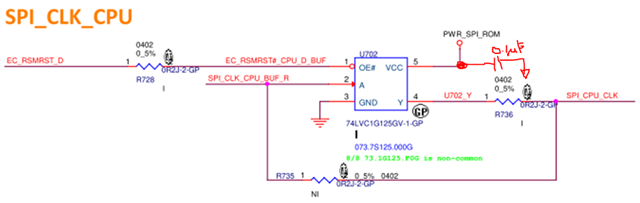

请注意、R735为 DY (下面的一个)。

所有信号电平为1.8V。

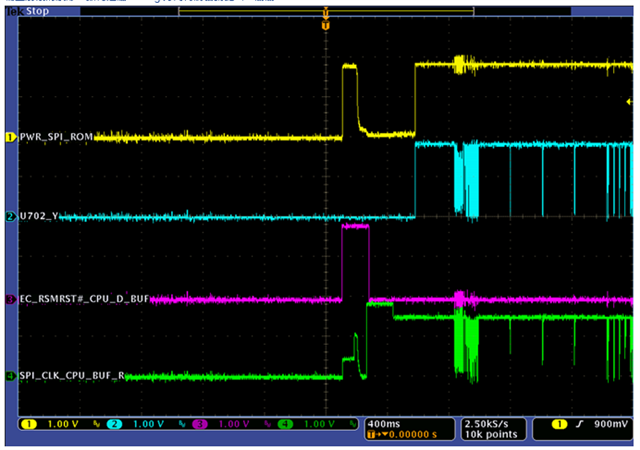

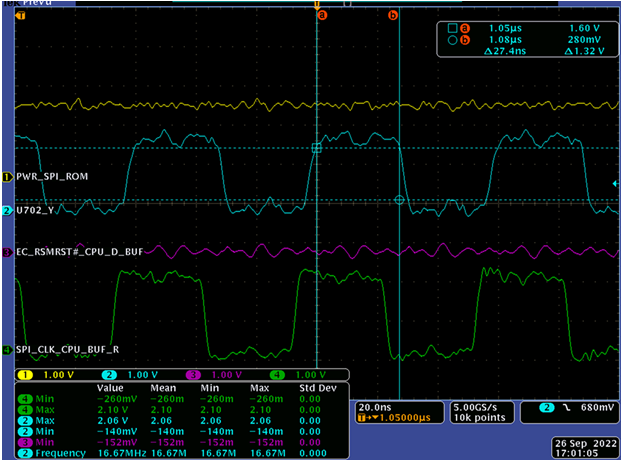

您可以看到蓝色和绿色是输入和输出,它们的行为与时钟信号不一样,

他们说、没有缓冲器、输入信号的行为正常、而且 Nexperia P2P 74LVC1G125也不会出现这种问题。

请帮助检查、谢谢

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

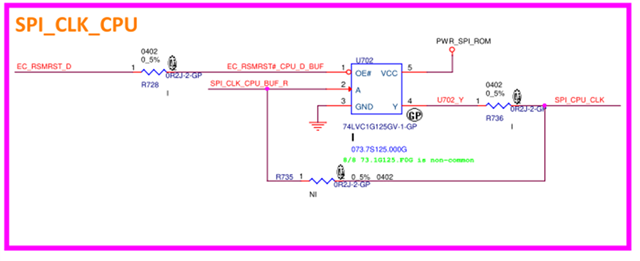

大家好、

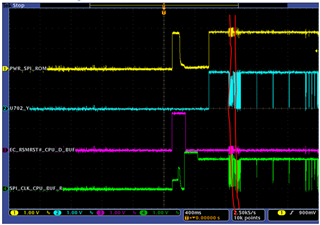

我的客户发现在使用缓冲器时没有时钟信号、

请注意、R735为 DY (下面的一个)。

所有信号电平为1.8V。

您可以看到蓝色和绿色是输入和输出,它们的行为与时钟信号不一样,

他们说、没有缓冲器、输入信号的行为正常、而且 Nexperia P2P 74LVC1G125也不会出现这种问题。

请帮助检查、谢谢

您好、Fred、

地面上似乎有相当多的噪声:

我建议在器件附近添加一个良好的去耦电容器。 如果它们已经有一个、则该系统可能需要额外的去耦。

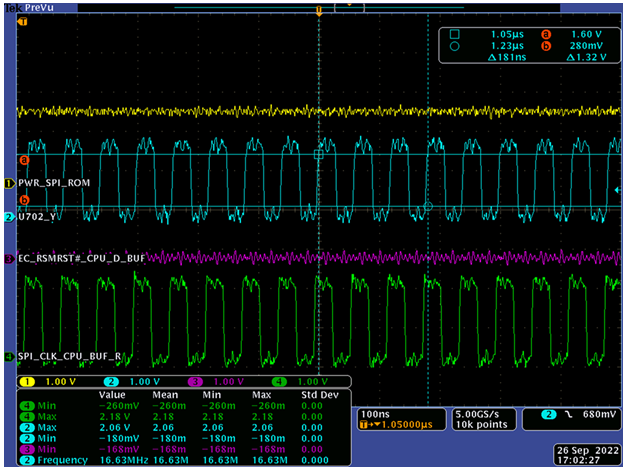

从这个角度来看-输入和输出看起来相当相似。 我们能否获得一个示波器截图、将 TI 器件与放大后的 Nexperia 器件进行比较、以显示实际时钟数据速率(周期似乎小于1ms、但时间刻度为每分段400ms)。 具体而言、我希望获得该区域的良好示波器截图、但放大到了小得多的比例(最好是100ns/div 或更小、但如果需要捕获波形、可以使用更大的比例):

您好、Fred、

抱歉-我应该说"旁路"电容器而不是"去耦"电容器。

请原谅我的不良作品:

应为"0.1uF"

在逻辑器件的电源引脚上放置一个旁路电容器应该是标准做法。 以下是要求它们的详细说明: [常见问题解答]如何为 CMOS 逻辑器件选择旁路电容器?

您好、Fred、

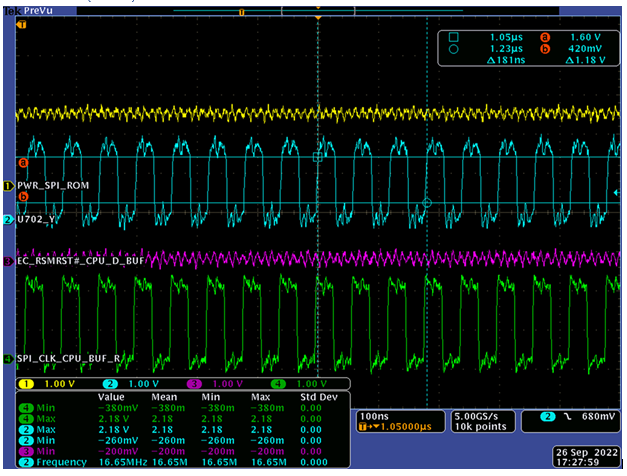

我同意 Clemens 关于示波器镜头的观点-这里的测量误差看起来存在失真。 我建议对缓冲器的输入信号进行触发、并将时间刻度设置为100ns/div、以便我们可以更详细地了解信号。

他们很可能只是将 LVC 器件推向极限、而 Nlia 器件在这批器件上的驱动力可能会稍强一些、因此它的工作"足够好"、不会导致问题。 我建议切换到 针对1.8V 运行进行了更优化的器件、例如 SN74AUC1G125。

尊敬的 Emrys:

很抱歉、我不 是要给您的建议打折扣、只是想详细了解您的理论背后的原因。

根据他们的说法,东芝不仅仅只有一个案例,它通过 了所有100个电路板。

回到原来的状态,我担心在输出端添加去耦电容器会减慢整个信号的速度吗?

因为在这种情况下、如果您怀疑我们的器件中的驱动器较弱、增大 CL 可能会变慢?

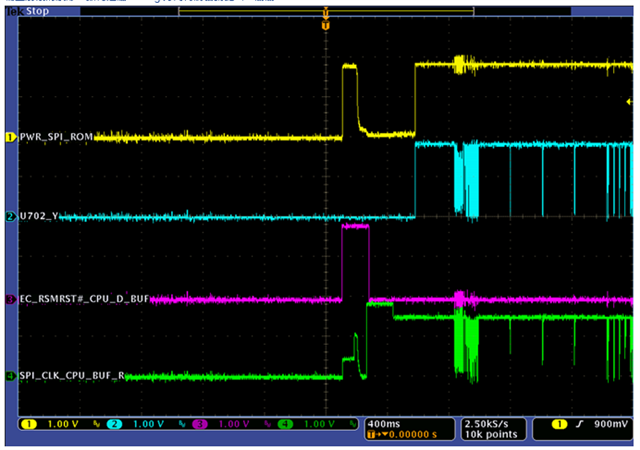

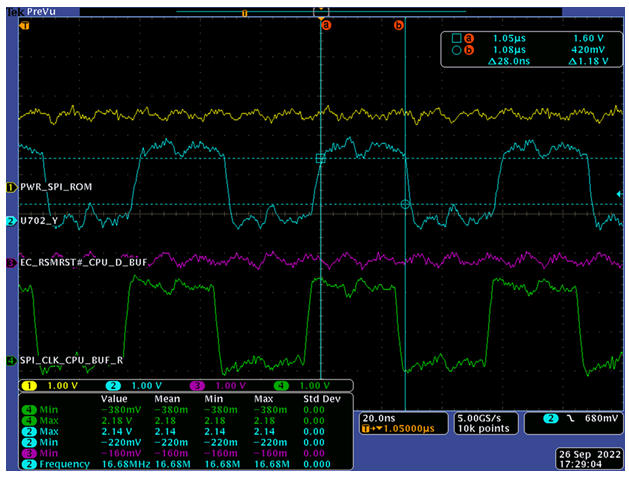

更新更多放大范围、请帮助检查差异。

TI 器件:

上升时间= 3.866ns、下降时间= 3.2ns

东芝器件:

上升时间= 3.8ns、下降时间= 2.387ns

感谢 Fred、

根据其电源线上显示的噪声、我建议他们查看并可能添加更多旁路电容器。 有关可能需要多个电容器的原因的详细信息、请发送此常见问题解答: