您好!

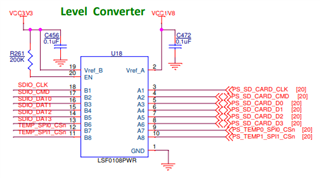

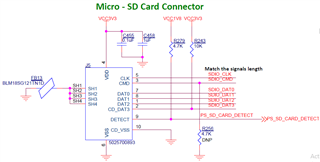

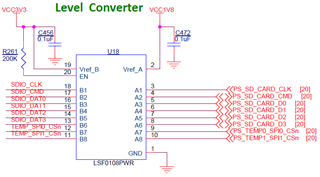

我们使用电平转换器(LSF0108PWR)将3.3V (Vref B)转换为1.8V (Verf A)、能够测量通道 A 信号逻辑电压为1.8V。 但在通道 B 中、对于 B6、B7、B8信号、信号逻辑电压为2.1而不是3.3V、其余的 B1、B2、B3、B4、B5通道信号逻辑电压为1.8V 而不是3.3V。

当我 将 EN (低电平)连接 到 GND 时、对于 B6、B7、B8信号、通道 B 信号逻辑电压为3.3V、其余 B1、B2、B3、B4、B5通道信号逻辑电压为0V、而不是3.3V。

请 验证以下原理图并建议是否需要任何更改。

此致、

Gajendran A