您好专家、

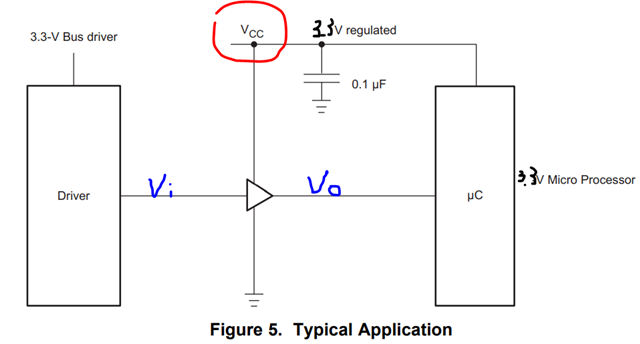

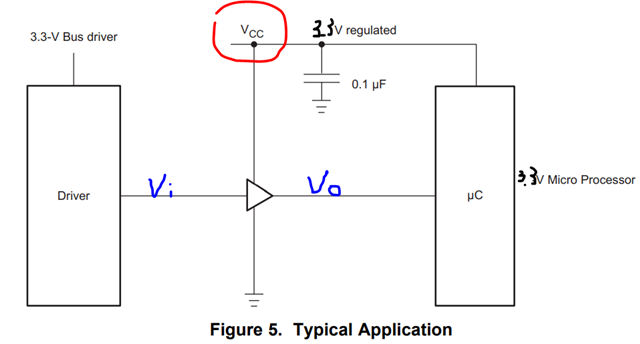

以下面的电路为例。

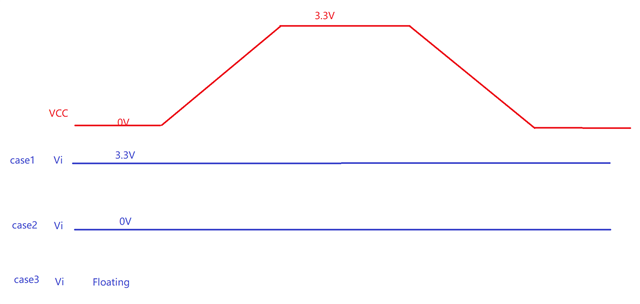

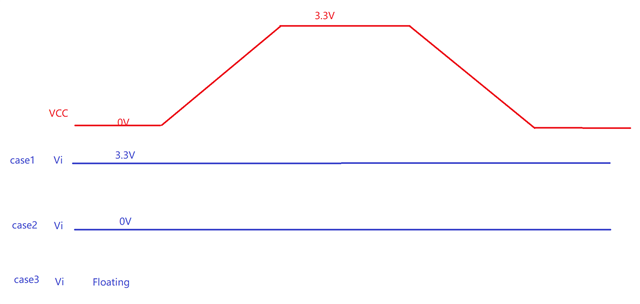

想要了解以下三种条件下的 Vo 行为和波形、尤其要注意:当 VDD 非常低时、内部 MOS 根本不起作用、Vo 的推挽行为输出是什么?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好专家、

以下面的电路为例。

想要了解以下三种条件下的 Vo 行为和波形、尤其要注意:当 VDD 非常低时、内部 MOS 根本不起作用、Vo 的推挽行为输出是什么?

您好!

当 VCC 设置为0V 时、这是一个定义的状态、输出处于高阻抗状态、这由数据表电气特性表中的 Ioff 规格定义。

VCC = 0V 和 VCC = 0.8V 之间的输出状态未定义、因此我无法保证这些值之间的运行。

话虽如此、我们希望输出保持高阻抗状态、直到内部电路偏置、偏置电压大约为0.5V。 之后、器件将像 CMOS 缓冲器那样工作。

高阻抗状态下的输出电压波形将完全依赖于输出负载和系统寄生效应。

器件通电时不要使 CMOS 输入悬空-此处提供更多信息: [FAQ]慢速或浮点输入如何影响 CMOS 器件?

您好!

我不知道盒装区域会说什么。 当输入处于"高电平"状态时、您是否尝试检查器件输出级的状态? 当器件断电(无 Vcc)或尚未偏置(小于0.5V)时、您如何知道这一点是否成立?

在盒装输入期间、您如何知道输出电压?

当电源关闭时、输出处于高阻抗状态、这与上面显示的低电平状态不同。

什么将输出驱动为低电平? 如果没有任何东西驱动输出、您如何知道该节点处的电压?

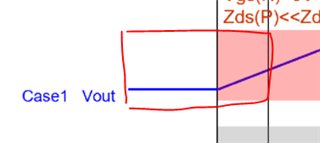

情况1输出看起来更像:

情况2和3有类似的问题--电压不是0V,但在断电/高阻抗状态期间是未知的。 此外、如果输入悬空、则输出将完全未知、但通常处于以下三种状态之一:高电平、低电平或振荡。 我不确定您是如何确定浮动 VCC 为~0.5VCC 的,但在实际系统中,浮动意味着“未知”,也就是说您无法为其分配值。 解决方法是不将输入保持悬空状态。

大家好、感谢大家耐心地阅读并提供建议。

请在 下面查看我的回复:

[引用 userid="216259" URL"~/support/logic-group/logic/f/logic-forum/1031459/sn74aup1g34-power-on-and-power-off-behaviors-of-output/3815900 #3815900">我不确定盒装区域是想说什么。 当输入处于"高电平"状态时、您是否尝试检查器件输出级的状态? 当器件断电(无 Vcc)或尚未偏置(小于0.5V)时、您如何知道这是正确的?[/quot]是的、当输入绝对高电平时、我尝试检查输出状态。 我可以理解您的顾虑 、但我假设我的输入为0V 或3.3V、即使 Vcc 尚未偏置。

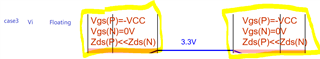

我还假设该 CMOS 电路中的所有元件都是理想的、 NFET/PFET 完全对称、这意味着不考虑寄生 和系统泄漏。 也就是说、分压点"Vout"实际上由 PFET 和 NFET 的阻抗(我在这里标记为"ZDS (P)/ZDS (N)")决定。 漏极和源极之间的阻抗实际上将由 CMOS PFET 器件的 Vgs 决定。

即使 Vgs 非常低、<Vth、无法打开器件通道、但它会影响源漏之间的有效阻抗、泄漏电阻 也会有所不同。 这就是为什么您可以在理论上看到"Vout"而不是"unknown"的清晰输出。 您可以在 VIRTOSO 软件中进行验证。

[引用 userid="216259" URL"~/support/logic-group/logic/f/logic-forum/1031459/sn74aup1g34-power-on-and-power-off-behaviors-of-output/3815900 #3815900"]我不确定您是如何确定浮动 VCC 为~0.5VCC 的、但在实际系统中、浮动意味着"未知"-即您无法为其分配值。 解决方案是_不将输入保持悬空_。[/quot]我同意您的看法、我无法确定浮动输入为~0.5VCC、我只是假设我的输入始终遵循此处的0.5VCC 进行分析。