大家好、

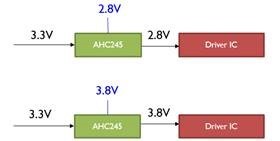

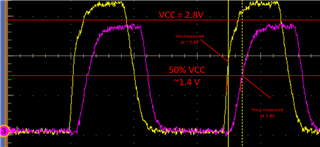

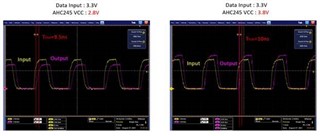

我想检查数据表中的 tPLH 和 tPHL 参数。 我在数据表中找到下表。 这些参数似乎与 PCB 布线上的 Vcc 和 Cload 有关。

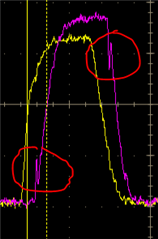

下面是我们的测量值。 我们直接测量 SN74AHC245引脚排列。(输入和输出)延迟时间约为10ns。 它可以满足数据表中显示的最大值、但我们直接测量引脚排列。 这是否意味着我们的 Cload 远小于15pF?

下面是我的问题。

根据我们的测试结果、您认为这是合理的

2.我们如何定义 Cload? PCB 迹线上的等效电容器? 如果我们直接测量引脚分配、我们可以说 CLoad = 0吗?

罗伊