https://e2e.ti.com/support/logic-group/logic/f/logic-forum/1024426/txu0204-q1-partial-power-down

器件型号:TXU0204-Q1大家好、

我对 P21 9.3.5数据表中的描述有疑问、如下所示。

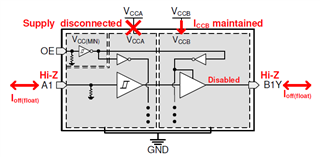

'建议在悬空(断开)任一电源之前、输入保持低电平。'

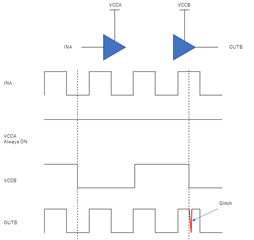

在我的系统中、VCCA 在 VCCB 打开和关闭周期期间处于活动状态。 在 VCCB 打开和关闭周期的同时、Ax 输入有可能由 MCU 驱动。

您提出建议的原因是什么(输入在浮动前保持低电平)?

可以在 VCCB 周期打开和关闭时切换输入(Ax)吗?

此致、