主题中讨论的其他器件: SN74AUC125、 SN74AUC34、 SN74AUC32

大家好

我的客户 不确定如何读取 SN74AVC4T234的数据表规格:

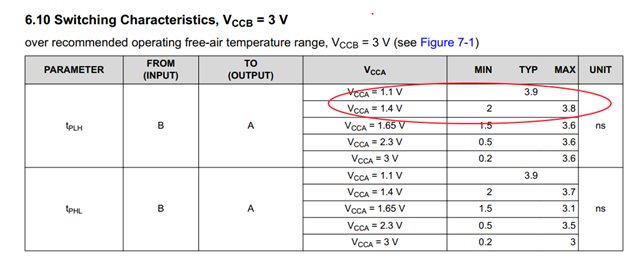

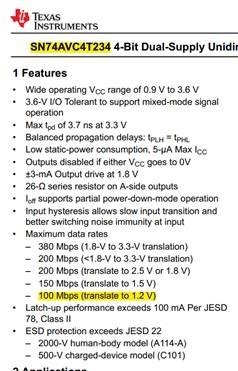

在数据表中、它们发现1.2V 时为100Mbps。

在其设计中、它们具有80MHz 时钟和数据(DDR、表示时钟上升沿和下降沿的数据变化)、由此产生的每通道160Mbps 数据速率将由电平转换器处理。

它们是否由于80MHz 时钟而在100Mbps 的规格范围内,或者它们是否由于160Mbps 数据速率而高于最大值?

此致

Ueli

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好

我的客户 不确定如何读取 SN74AVC4T234的数据表规格:

在数据表中、它们发现1.2V 时为100Mbps。

在其设计中、它们具有80MHz 时钟和数据(DDR、表示时钟上升沿和下降沿的数据变化)、由此产生的每通道160Mbps 数据速率将由电平转换器处理。

它们是否由于80MHz 时钟而在100Mbps 的规格范围内,或者它们是否由于160Mbps 数据速率而高于最大值?

此致

Ueli

您好 Clemens

以下是客户反馈:

--------------------

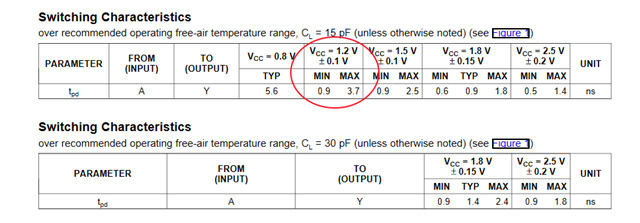

他们发现、AUC 在电源电压方面比 AVC 要快、这一点并不清楚。 进一步低于 TPD 响应 将复制 AUC34和 AVC4T234的 TPHL/TPH 值。 只有100 - 200ps 的差异。 此外、未为 AUC 器件指定最大数据速率。 考虑 到 AUC 的额定电压为1.2V (CL=15pF/2kOhm)和 AVC (CL=30pF/500ohm)、似乎没有区别。 它们必须根据 最大值进行设计。

--------------------

请评论他们的理解是否正确。

此致

Ueli

SN74AUC32

SN74AVC4T234