主题中讨论的其他器件: SN74LVC2T45、 SN74LVC2G17

大家好、

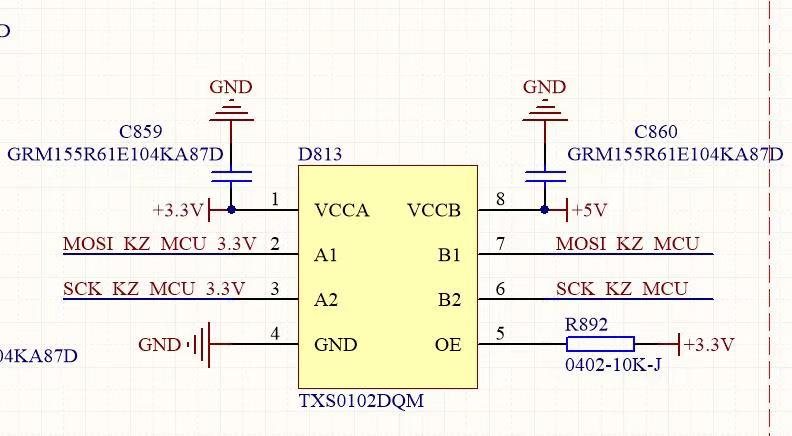

我的客户正在测试 TXS0102。 原理图如下所示。 B1 B2是输入引脚、它们来自5V MCU。 A1 A2是3.3V MCU 的输出引脚。 B2—>A2是 SPI 接口的 clk 信号,B1—>A1是 SPI 接口的数据信号。

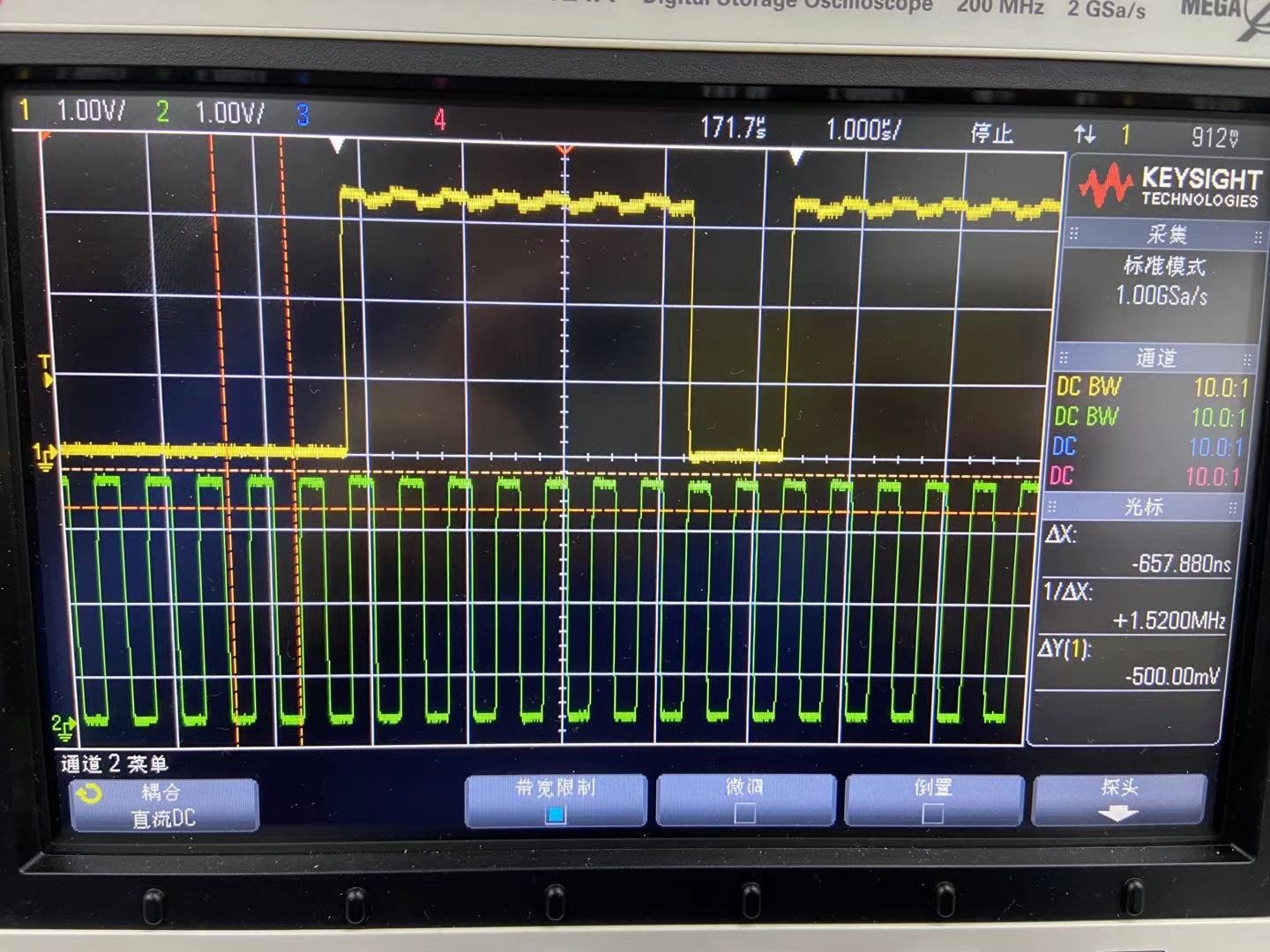

我们测量了 A1和 A2引脚上的信号、如下所示。 CH1=A1引脚=数据信号。 CH2=A2引脚=CLK 信号。 我们发现数据信号在高电平期间不稳定。

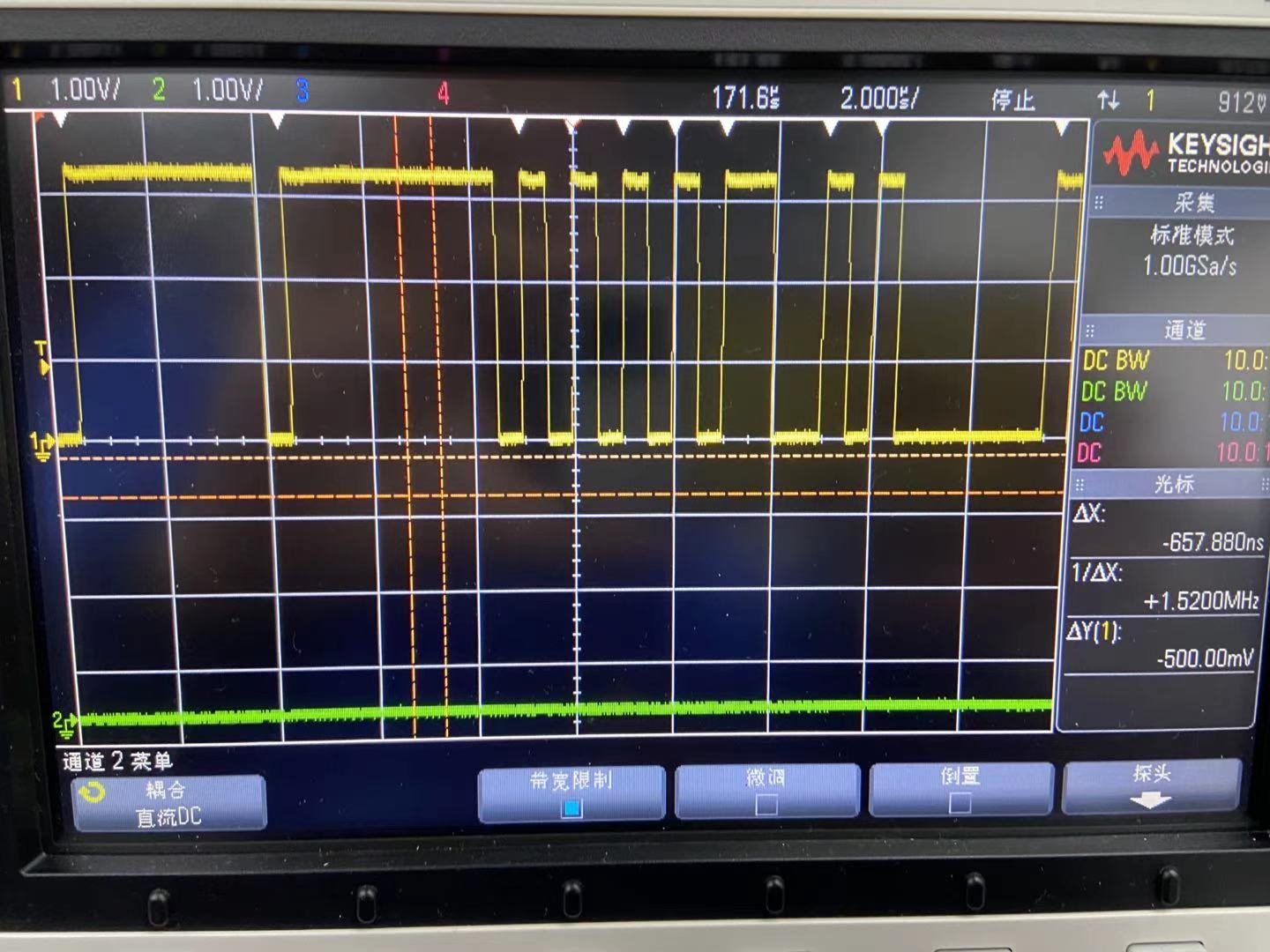

然后、我们从5V MCU 到 B2引脚断开 CLK 信号、只让数据信号从 B1—>A1经过。 然后、我们测量了 A1上的输出数据信号、如下所示。 数据信号在高电平期间变得稳定。

因此、根据上述测试、通过 TXS0102的 clk 信号对其相邻数据信号的影响似乎很小。 那么、您对为什么会发生这种情况有什么建议吗? 谢谢。

顺便说一下、3.3V 和5V 电源都来自 LDO、这两个 LDO 非常稳定。

此致、

韦恩