大家好、

对于3.3V 工作电压、数据表规定了1.5ns 的最短保持时间 、但 SRCLK 至 QH'的最短保持时间为1ns。 如果我们将其中一个的输出连接到另一个的输入、这是否会违反下游器件的最小保持时间? 如果是、还有哪些其他方法可以解决这种违规问题? 或者、由于上游器件必须具有最短1.5ns 的保持时间、下游器件实际上被保持在最小1.5ns+1ns、因此不会发生任何违反?

谢谢、

Ishraq

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

大家好、

对于3.3V 工作电压、数据表规定了1.5ns 的最短保持时间 、但 SRCLK 至 QH'的最短保持时间为1ns。 如果我们将其中一个的输出连接到另一个的输入、这是否会违反下游器件的最小保持时间? 如果是、还有哪些其他方法可以解决这种违规问题? 或者、由于上游器件必须具有最短1.5ns 的保持时间、下游器件实际上被保持在最小1.5ns+1ns、因此不会发生任何违反?

谢谢、

Ishraq

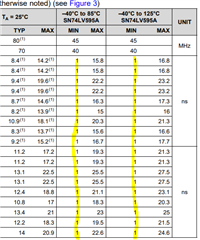

最小延迟中的"1ns"大于实际规格的占位符--它比将其留空或置零更好,但它并不 表示 器件可能只能在1ns 内转换。 请注意、这在整个电路板上是相同的:

即使在最大电压下处于完美条件下,我也不会期待低于2ns 的延迟--如果是这样,那么另一个器件也会在相同条件下运行,并且运行速度也会更快。

菊花链式移位寄存器的主要问题是确保您要么同时触发移位寄存器、这正是它们的设计目标、要么首先触发链中的最后一个器件、以避免出现任何时序问题。 这可以通过使用布线长度或缓冲器来增加延迟来实现。 通常、只有非常大型的设计才需要后一种选择(例如、考虑在几米范围内控制数千个 LED 的巨大标志)。