Other Parts Discussed in Thread: TIDA-01509

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LV165A 主题中讨论的其他器件:TIDA-01509

尊敬的先生:

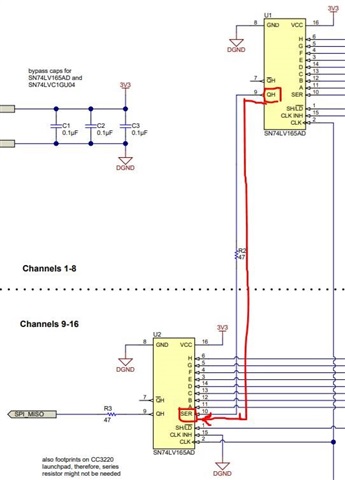

根据 TI 参考设计(TIDA-01509、 https://www.ti.com/lit/pdf/tidrvh7)、U1 QH 引脚连接到 U2 SER 引脚。

我想知道一个串行输出 QH 与另一个寄存器的串行输入 SER 之间的布局长度限制是多少。

在布局设计时、我们是否需要考虑传播延迟?