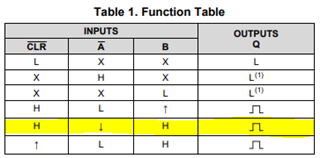

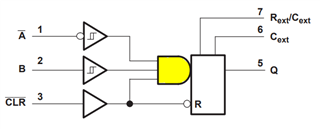

对于此 IC 的输入/A、我们必须定义默认状态。在操作中、我们为/A 信号提供50Hz 频率 、其中 B 和/CLR 信号处于高电平。 我们必须在/A 上拉或下拉信号、以便该 IC 的输出 Q 处于低电平。换句话说、我们必须定义 Q 应为低 电平的默认状态。

当我们将具有 B 和/CLR 信号的/A 信号拉至高电平时、您能不能指导我们、那么输出 Q 的状态是什么? 因此、基本而言、为了确保输出处于低电平、我必须设置的/A 信号的状态应该是什么(低电平或高电平、需要从控制器供电)、其中 B 和/CLR 信号处于高电平-这两个信号上存在上拉电阻。