https://e2e.ti.com/support/logic-group/logic/f/logic-forum/874433/sn74v293-unexpected-offset-value

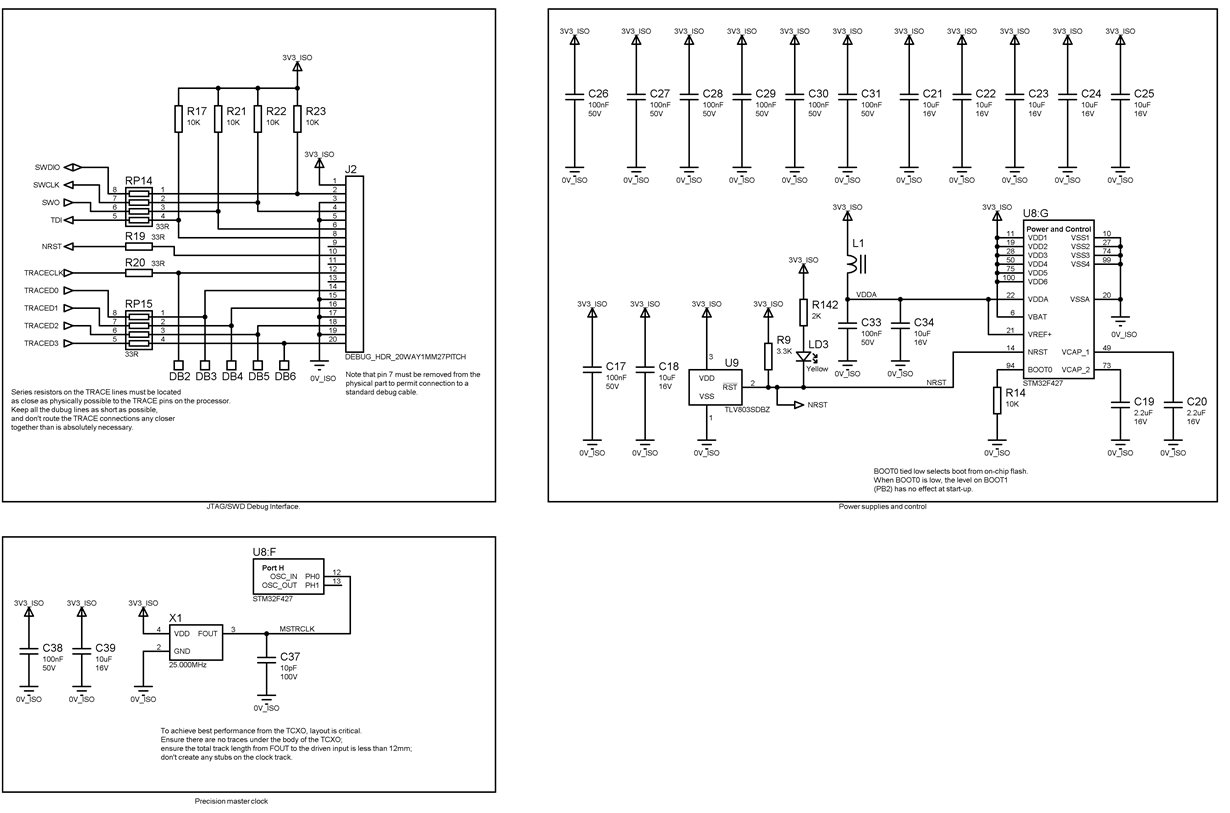

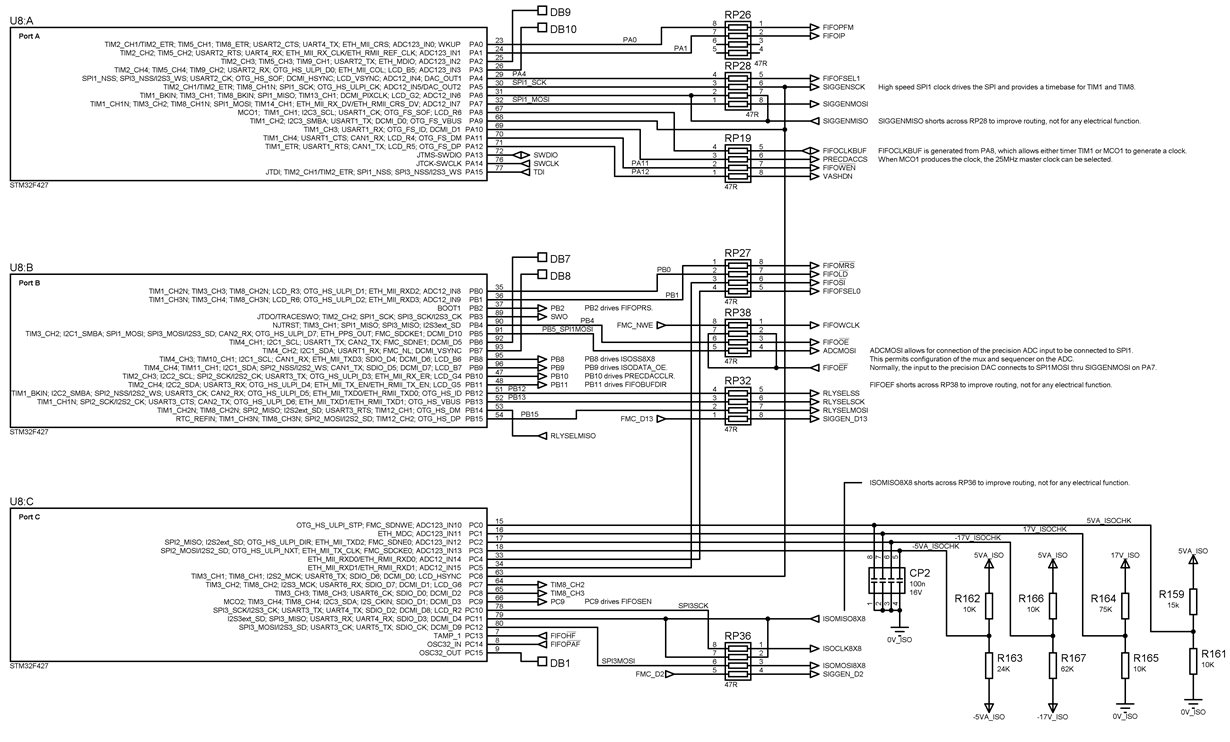

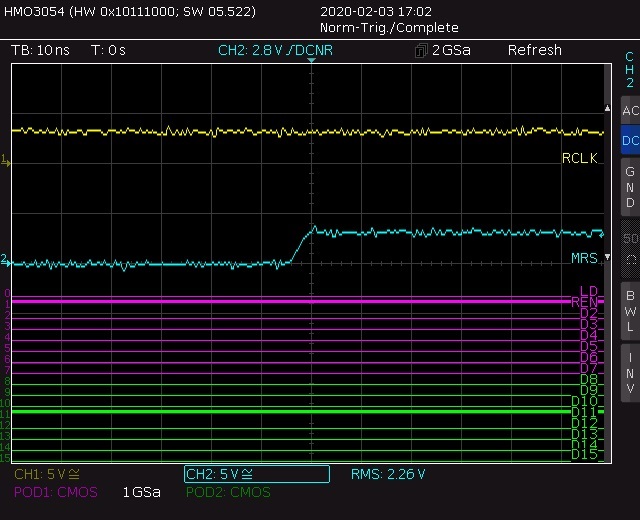

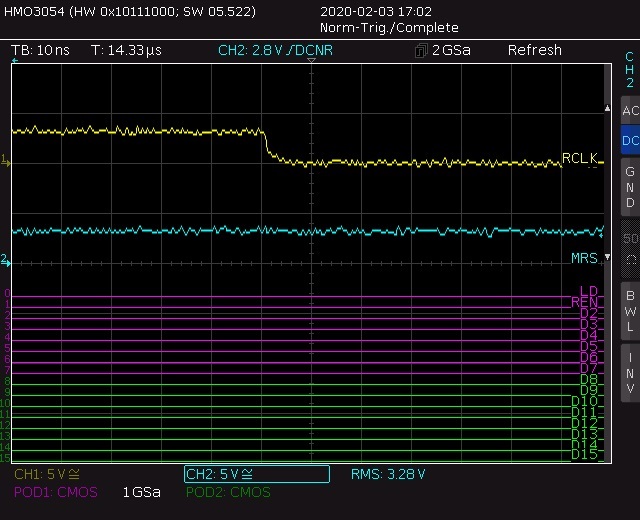

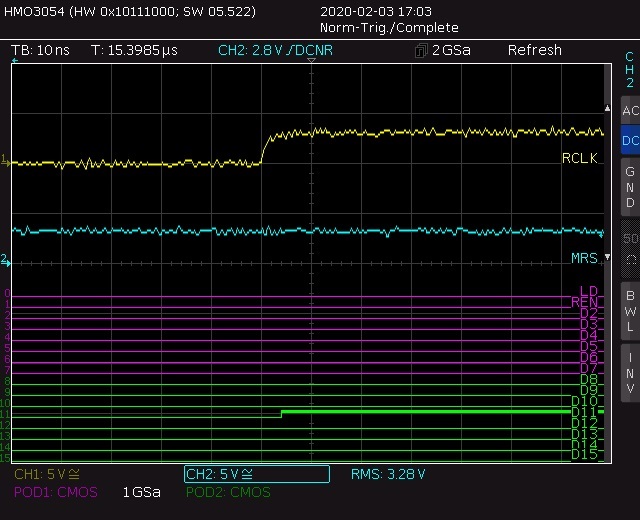

器件型号:SN74V293我有许多包含'V293 FIFO 的原型板。 在配置过程中、固件会验证组件上的组件、包括 FIFO 的运行情况。

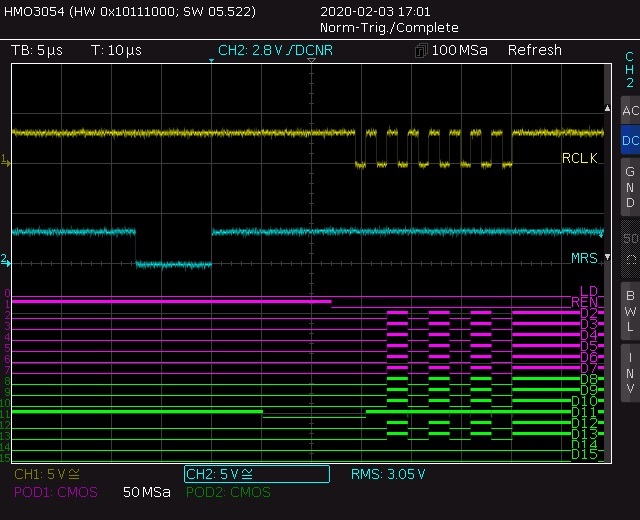

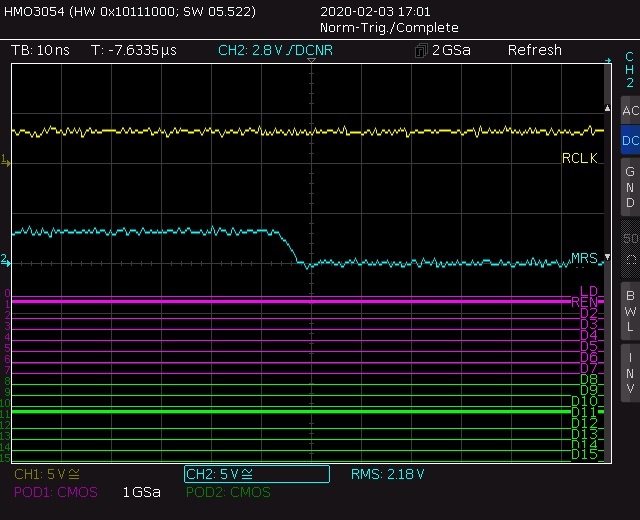

原型的前一版本(使用'V293s、部件标记为74COS9TG4)运行正常、并返回预期的空和满偏移寄存器值。 在此应用中、使用引脚搭接将两个偏移值设置为16383。

原型的最新版本组装有器件标识为84AZVETG4的器件、会返回两个偏移的不同值:空偏移不正确(其值因运行而异)、但完整偏移始终是正确的值。

这些器件的特定批次是否存在任何已知问题?