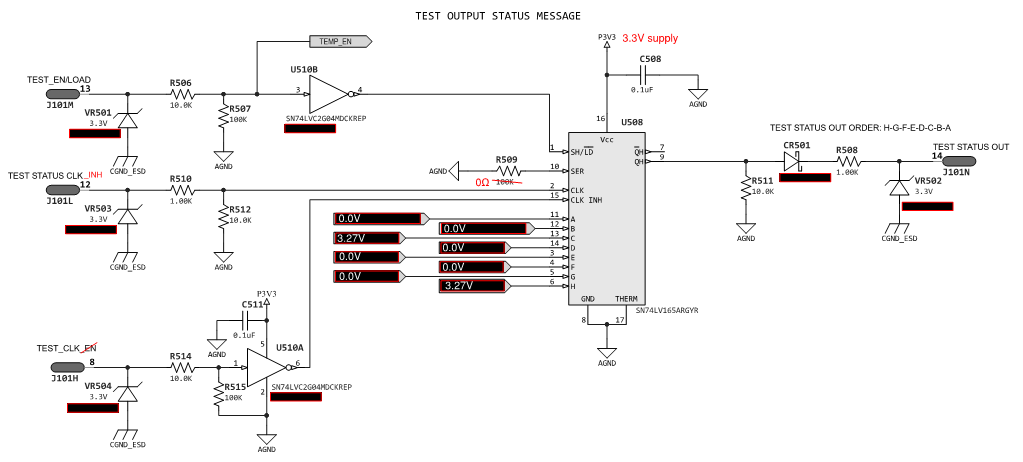

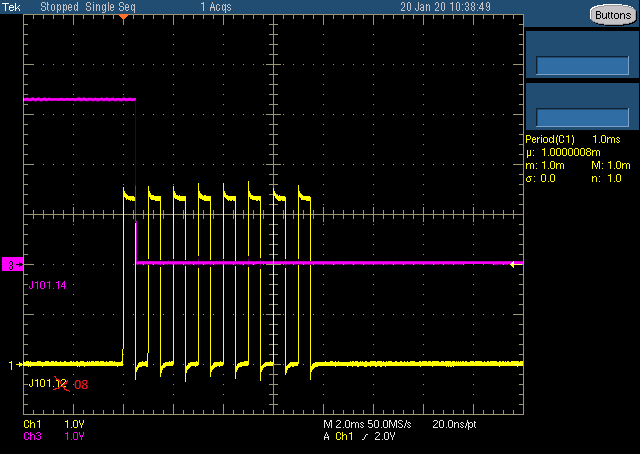

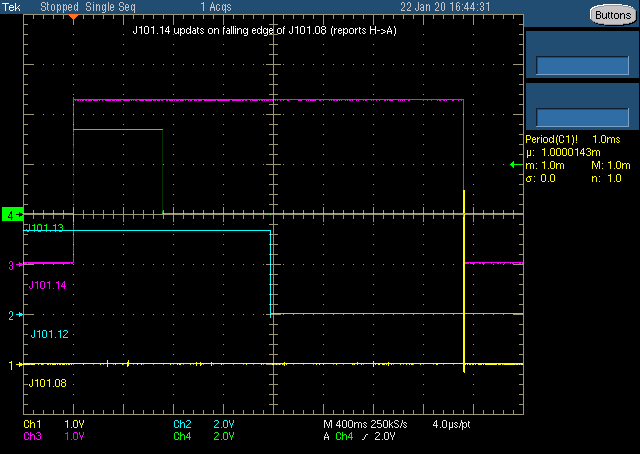

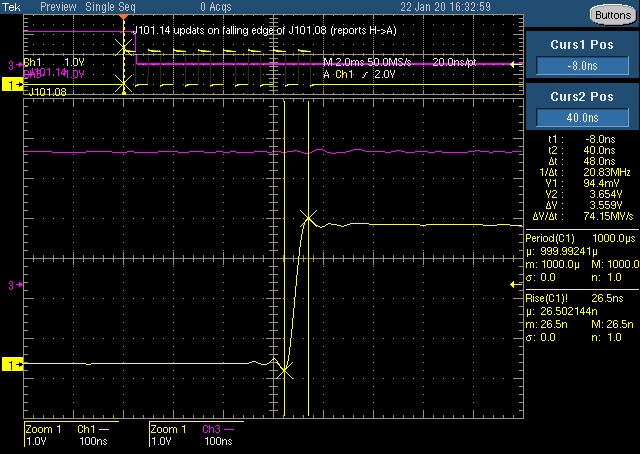

我在其中一个原型设计中使用 SN74LV165A、无法获取 Q_H 或\Q_H 输出以更改状态。 Q_H 保持低电平、而\Q_H 保持高电平。 在这种情况下、我的两个并行输入设置为高电平、其余输入设置为低电平、同时 SER 也被拉低。 我已将\LD 引脚低电平发送~1秒、然后将我的8个时钟脉冲(1ms 50%占空比)发送到 CLK 引脚(同时 CLK_INH 设置为低电平)。 但输出不会改变状态、而是保持静态。 到目前为止、我已在3个器件上尝试过相同的结果。 我唯一能想到的是低 SER 输入在某种程度上覆盖了并行 H-A 输入、但我在数据表中看不到与此类内容相关的任何内容(除了\LD 保持低电平与 CLK、CLK_INH 和 SER 状态无关的第一页)。

上电后、我第一次发送\LD 脉冲时、Q_H 从低电平变为高电平。 然后、当发送 CLK 脉冲时、Q_H 从高电平变为低电平并保持该状态。 我已经尝试过各种时钟脉冲宽度、但对输出没有影响。

如果能对产出为何不会改变有任何了解,将会受到极大的赞赏。