尊敬的专家:

我的客户正在评估 SN74LVC123并遇到问题。

如果您能提供建议、我将不胜感激。

--

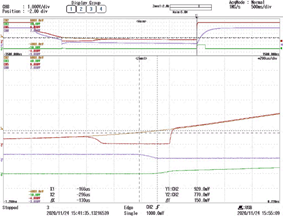

在 SN74LVC1G123DCUR 中、一个大约80ms 的脉冲信号由输出端子 Q 输出、电压为0.93V

在 Vcc = 0V 至5V 的路上。

(在系统中、由于输出信号的影响、后续级的电路将运行。)

(1)请你告诉我们造成这种现象的原因。

(2)我们想知道 A、B 和 CLR 的边缘和下降沿是如何确定的。

您能看到波形和原理图吗?

e2e.ti.com/.../Question-about-SN74LVC1G123DCUR.xlsx

根据功能表、当 IC_B 或 CLR 从 L 转换到 H 时、可能会输出脉冲

但是、0.93V 超出工作额定值。

我们期待您的建议。

--

感谢您提前提供的出色帮助。

此致、

新一