设计

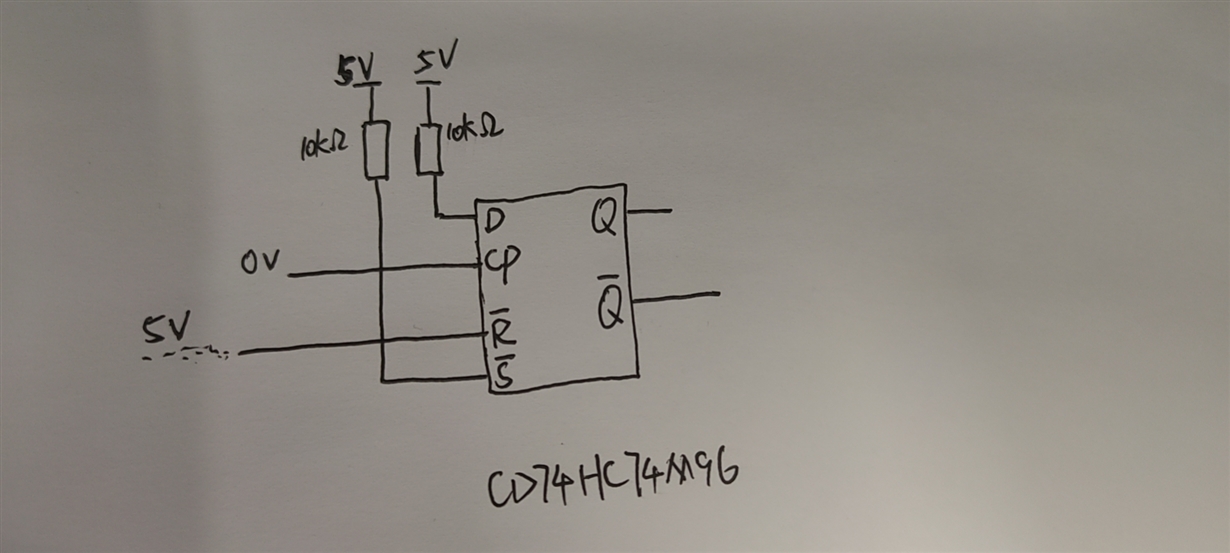

我们使用的是 CD74HC74M96 D 触发器芯片。 接线图如下所示。

芯片上电后、~R 和~S 引脚均被拉高。 根据真值表、Q 应该输出0V。 但在我用导电产品接触~S 引脚后、芯片的 Q 引脚将设置为5V (芯片的5V 电源)。 芯片置位后、用导电产品(例如示波器探针或一对镊子)触碰~R 引脚、芯片 Q 复位。

芯片上电后、~R 和~S 引脚均被拉高。 根据真值表、Q 应该输出0V。 但在我用导电产品接触~S 引脚后、芯片的 Q 引脚将设置为5V (芯片的5V 电源)。 芯片置位后、用导电产品(例如示波器探针或一对镊子)触碰~R 引脚、芯片 Q 复位。

我怀疑这是10K 上拉电阻器的问题、但在更改为2K 电阻器后仍然存在这种现象。 将10K 更改为0Ω Ω 后、问题不再出现。

这是我之前意外测试过的结果。

在对产品进行静电测试(静电枪对准电路板面板、面板上有放电电路)后、6kV 静电测试板将被重置。 将上拉电阻器更改为0Ω 可以暂时解决问题、但不清楚是什么原因导致导电产品将芯片复位、因此我想在设计电路时问您、 最好在上拉所有芯片时使用10K 或100K 电阻器、以防止芯片损坏(例如短路)、而不是直接导致电路板损坏。

我不确定 CD74HC74的内部输入上是否有任何弱上拉电阻。 我想就此向您咨询。