请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74HC164 大家好、

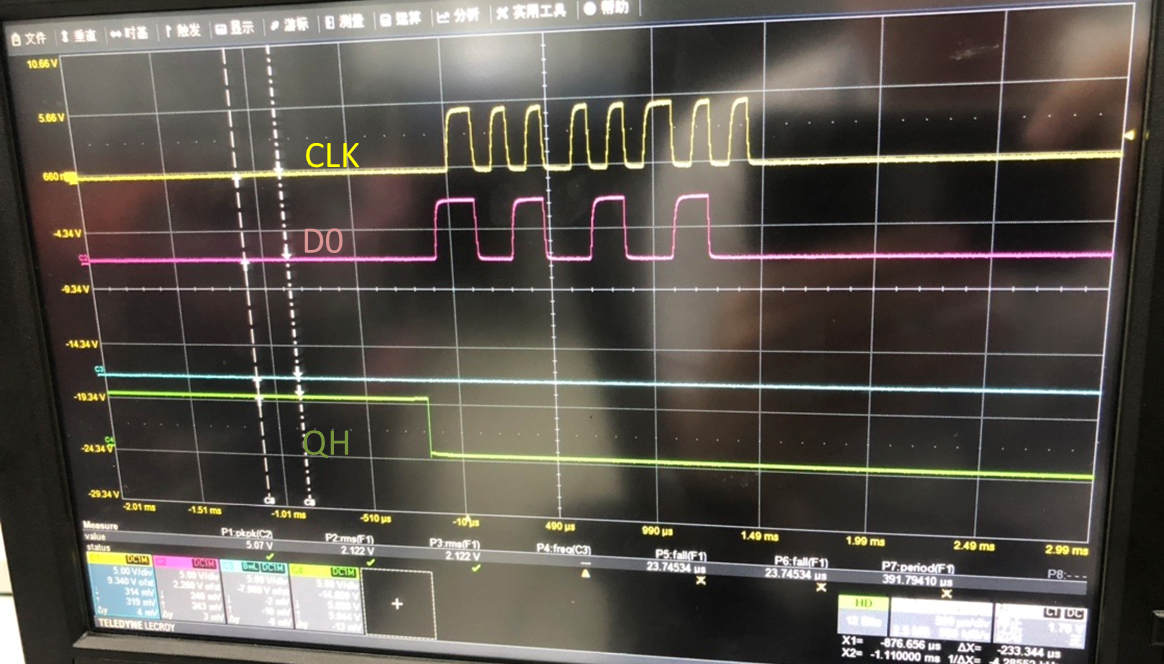

在这里了解您很高兴。 我的客户使用 SN74HC164来驱动 LED、原理图如下所示。 当我的客户向 LED_D0引脚输入10101010时、他们发现有时 QH 在 CLK 的第8个上升沿处于低电平(三个器件发现了此类问题)。 您能否帮助与我分享可能导致此类问题的原因? 谢谢。

BR、

查尔斯·林

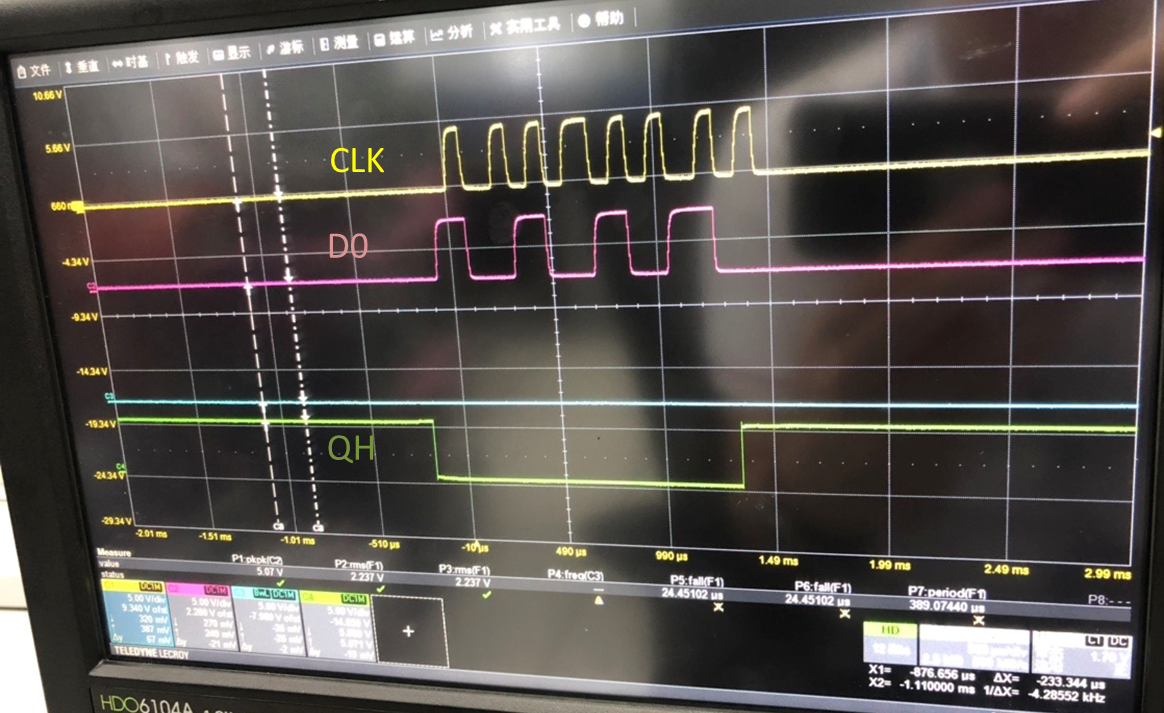

CLK/D0/QH 的右侧波形

CLK/D0/QH 的错误波形