https://e2e.ti.com/support/logic-group/logic/f/logic-forum/943342/cd4050b-cd4050b

器件型号:CD4050B主题中讨论的其他部件:CD4098B、 CD4013B

你好

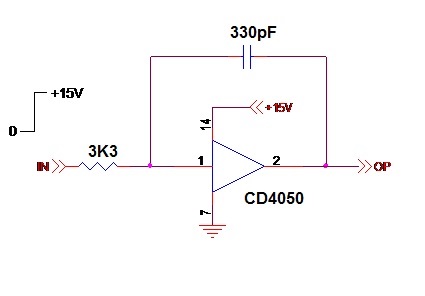

我希望使用以下 Cktt 为我们的三级逆变器创建最小脉宽。

每腿应使用四个此类 Ckts。 目标脉宽约为800nS 至1.1us

和关断时的电流。

PS 为+15V、输入信号也为0-15V。

我有以下问题:

在负转换点、输入将暂时拉至 GND 以下

其中、内部钳位二极管应通过 O/P 级的 Rdson 复位330pF 电容。

内部钳位二极管(至 GND)是否适合重复使用?

2.在正转换点、输入应高于+15V。

它是否会破坏重复脉冲?

3.如果我选择在输入端采用串联二极管,则任一端连接+15和 GND

但不要在330pF 电容器上插入限值电阻器、这是可以的吗?

谢谢、此致

瓦伦