主题中讨论的其他器件: LSF0108、 SN74LVC2G07、 LSF0102、 TINA-TI、 SN74LVC1G07

大家好、TI 逻辑器件论坛、

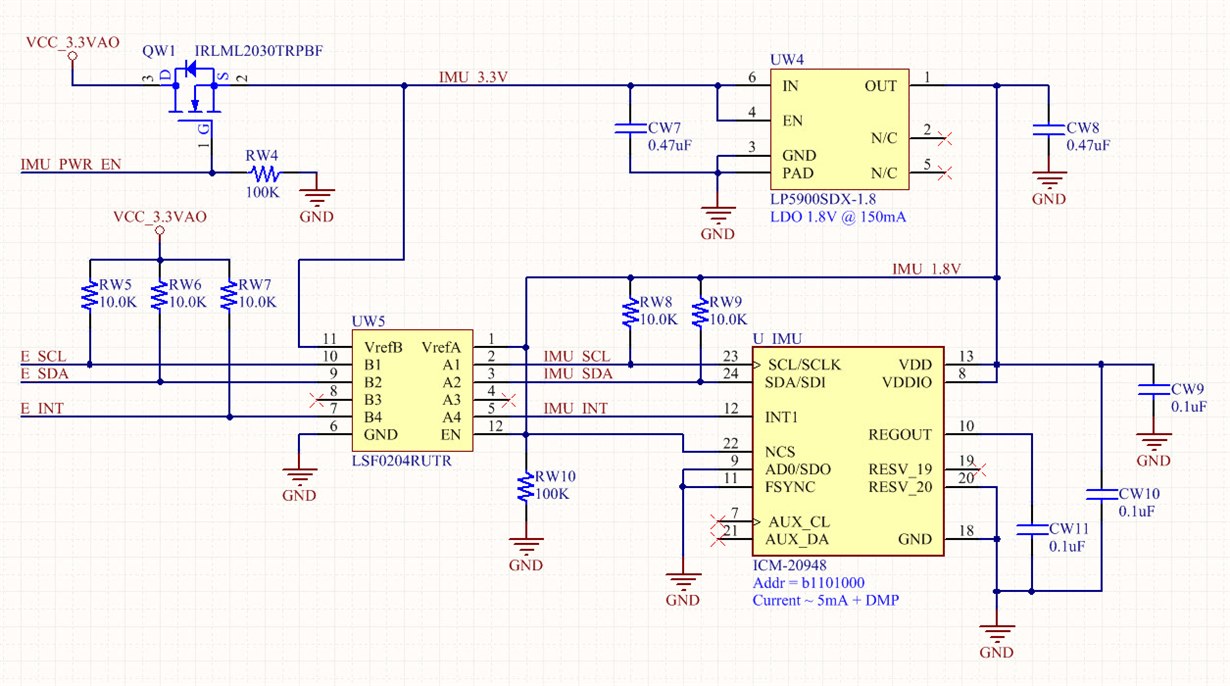

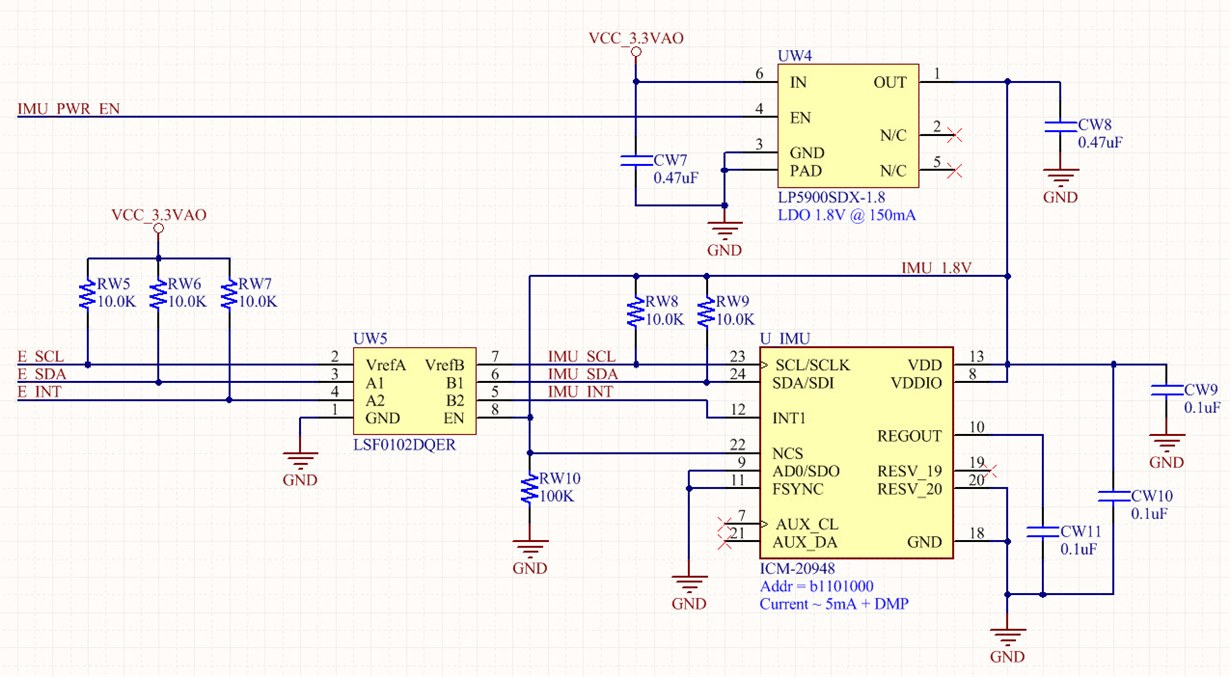

我需要在3.3V"始终开启"的处理器和通常将断电的1.8V 外设器件之间转换 I2C 总线和控制信号。 通过阅读 LSF0204上的其他论坛帖子、工程师报告说、由于 Vref_B 上的200K 内部电阻器和一般输入泄漏、A 和 B 端口之间存在显著的寄生功率泄漏(未供电电源轨上出现高达1V 的电压)。 这对我的设计来说是非常不利的。 我注意到、Ioff 仅在 Vref_A = Vref_B = 0的条件下指定、而不适用于单个未供电端口。 因此、我建议也使用原理图左上角的 NMOS FET 从 Vref_B 移除电源、而不是使用 IMU_PWR_EN 信号简单地禁用 LSF0204的1.8V LDO 和 Vref_A。 这样可以最大限度地减少泄漏吗?我要忽略的这种方法是否有任何缺点?

谢谢、

Steve C