请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G175 主题中讨论的其他器件:SN74AUP1G17

大家好、团队、

我们是否有下降沿时间的最短时间规格?

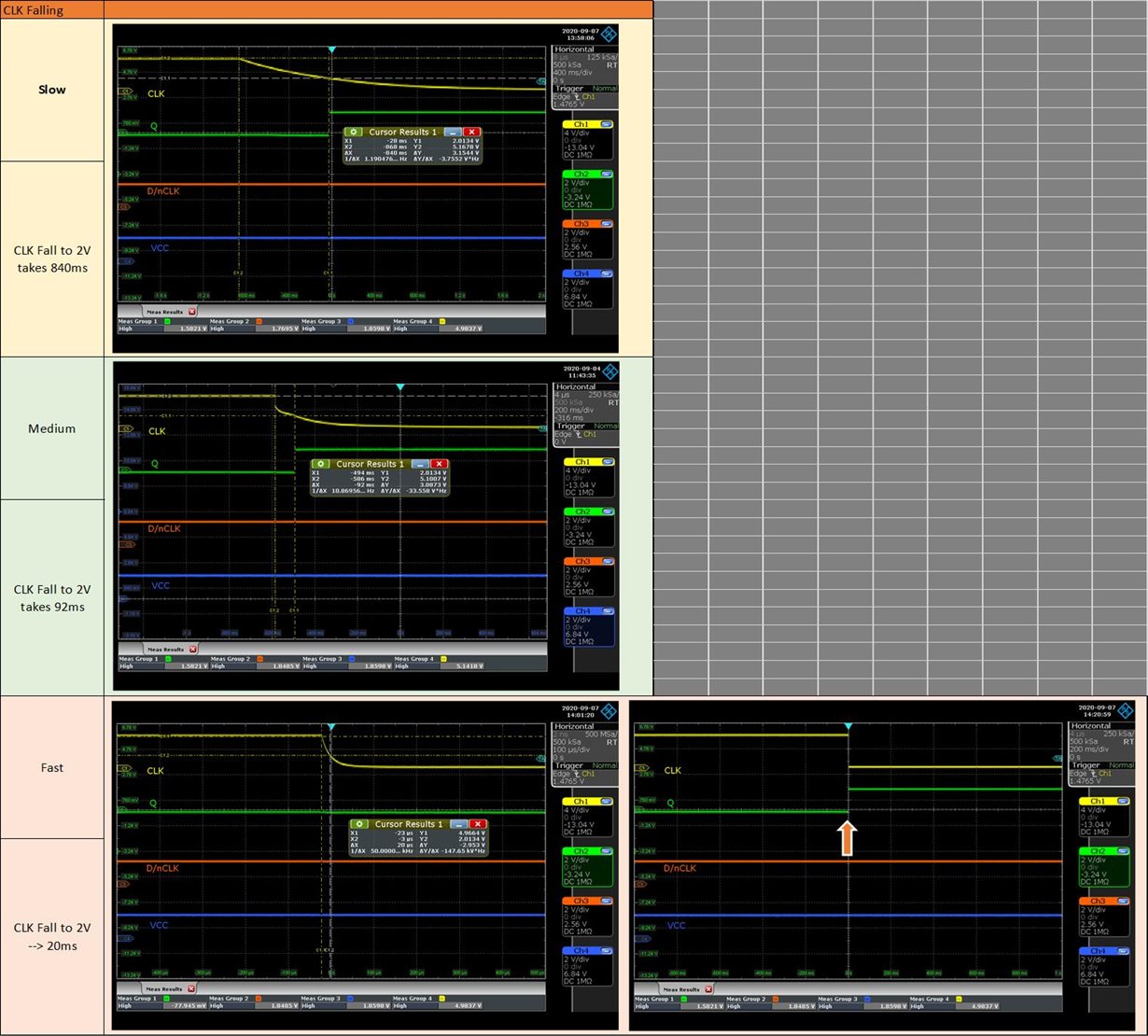

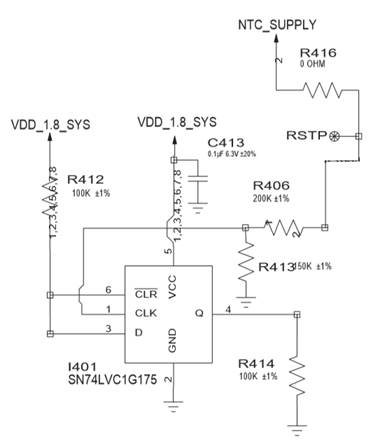

我们发现、如果 CLK 的下降时间更长、则会发生异常 Q 输出。 以下是 CLK 的三种下降时间(慢速/中速/快速)、在慢速/中速条件下、Q 输出总是出现异常。 但在快速条件下、CLK 下降5倍、只有 Q 有上升沿时才下降、大约20%以获得异常 Q 输出。 它可能与下降时间规格相关、以避免 Q 输出异常。 您是否能帮助确认它应该是什么下降规格? 原理图如下所示。 谢谢。

原理图:

此致、

罗伊