主题中讨论的其他器件: SN74LVC1G17、 SN74LVC1G14

您好!

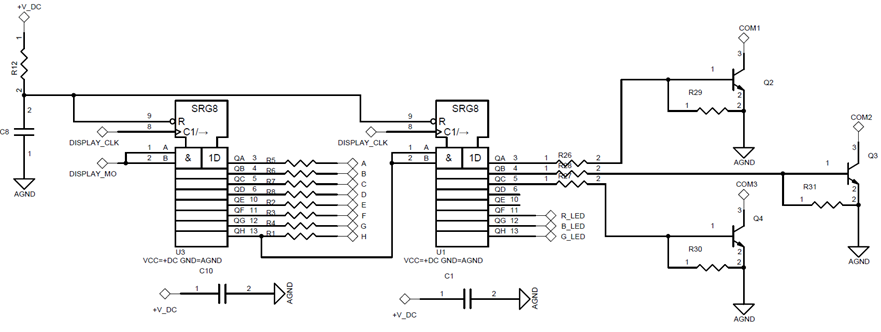

我客户的原理图如下:U3和 U1是两 个 SN74HC164。

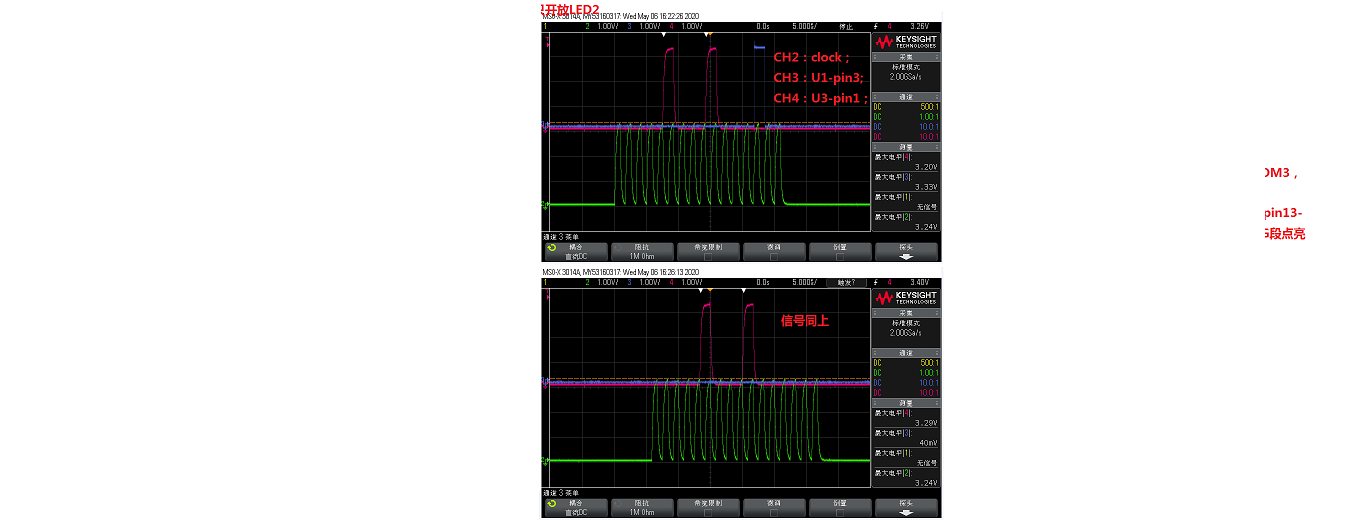

在正常电路板上、波形显示如下(上图)。 在不良电路板上、波形如下所示(下图)

通道2 -绿色。 U1-PIN3:蓝色 U3引脚1:紫色。

理论上、U1-PIN3应该是 U3-PIN1延迟的9个时钟。 在紫色线路上经过9个逻辑高电平的时钟后、蓝色线路上应该有逻辑高电平。 但在错误的电路板上、逻辑高电平消失。

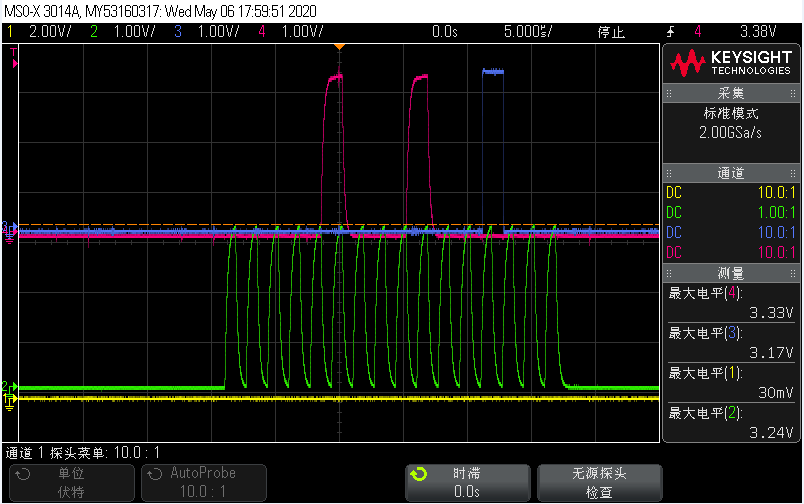

然后、我们在坏板上测量了波形、但现在我们测量的是 U1引脚1而不是 U1引脚3。 在 U3引脚1上经过8个时钟的逻辑高电平后、我们可以看到 U1引脚1上的逻辑高电平。

U1引脚1-蓝色、U3引脚1-紫色

因此、它显示了从 U1引脚1到 U1引脚3跳过了坏电路板上的逻辑高电平。

当我们使用两个不同批次 的 SN74HC164 9BATHQK 和9BAECSK 时、会发生该问题。 如果我们在 9BATHQK 或 9BAECSK 内使用同一批次、则不会出现问题。 该器件已在客户中使用了很长时间、这是我们第一次遇到此问题。

请您建议下一步做什么?