https://e2e.ti.com/support/logic-group/logic/f/logic-forum/921084/sn74lv4046a-sn74lv4046a

器件型号:SN74LV4046A主题中讨论的其他器件:CD74HC4046A

你(们)好

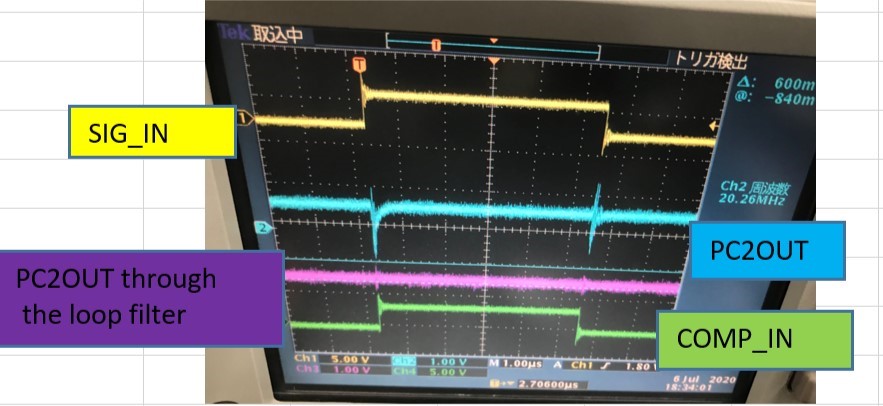

现在、我将其仅用作相位比较器(意味着我不使用其 VCO)。在我的批准中、在 cixo 时钟上还有另一个 VCXO。然后、当我将相同的 VCXO 时钟放入每个 SIGin 和 Comp_in 时、PCout 将如何工作?

换句话说、在我的批准中、由该 IC 控制的 VCXO 和使参考时钟处于相同状态。

非常感谢。