大家好、团队成员

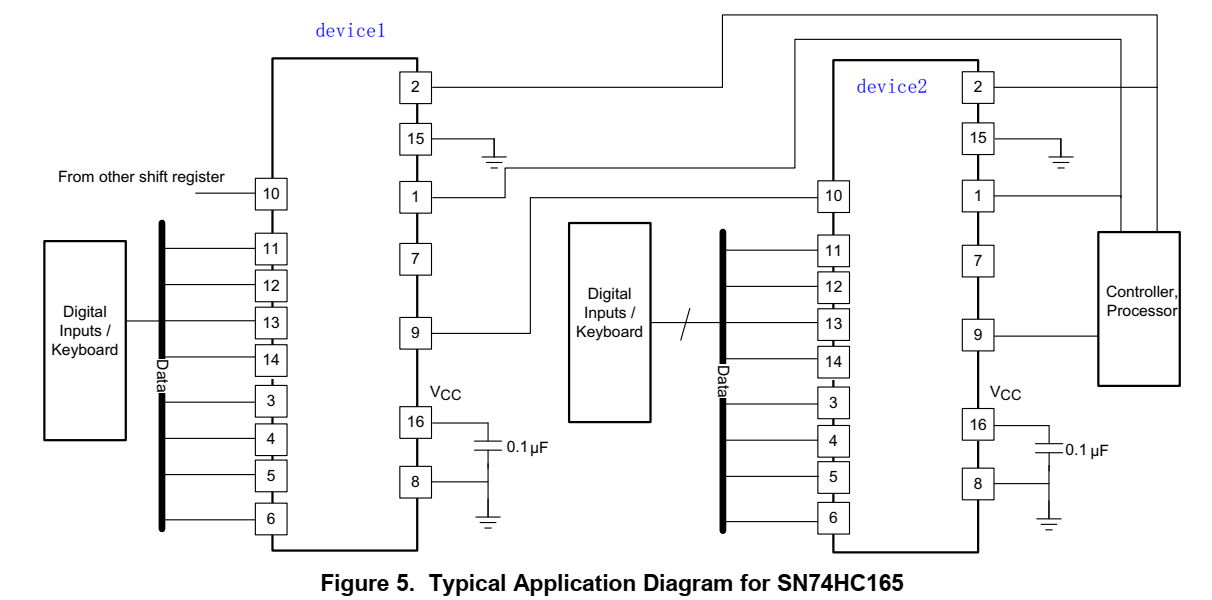

我的客户使用两个 PICS SN74HC165作为级联配置。 根据数据表指南、两个器件 CLK 应连在一起。

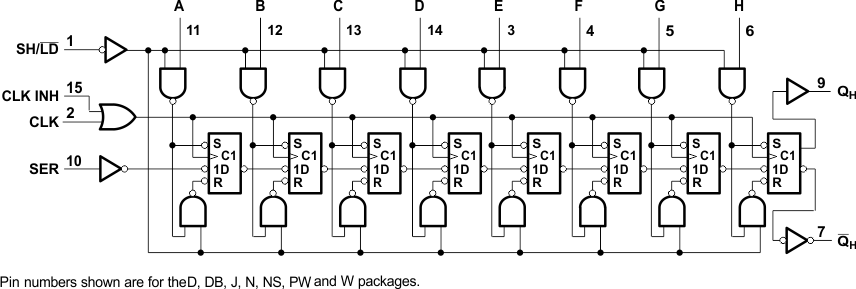

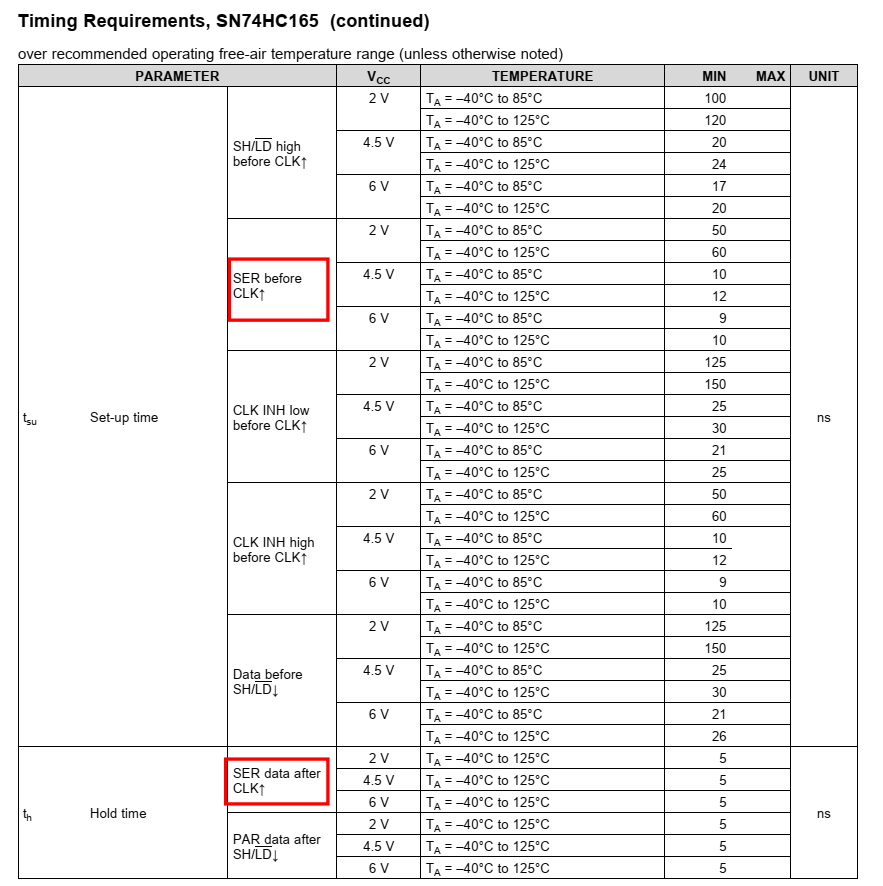

我对 device1通过 SER 引脚将其数据移动到 device2的时间序列要求有疑问。

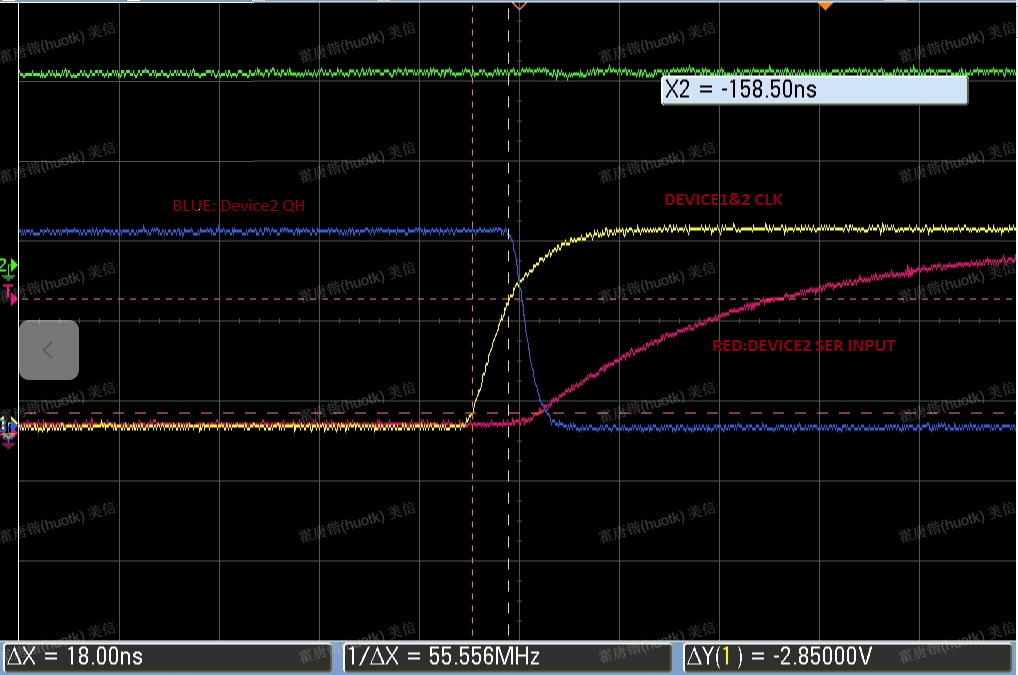

作为使用相同 CLK 信号的两个器件、这两个器件都将接收到一个边沿信号以触发单次触发移位行为。 在平均时间器件中、2也将开始移动 SER 引脚输入数据。 但由于 CLK 边沿和 QH 引脚信号输出之间存在延迟(它将是 device2 SER 引脚输入)。 因此、如果该延迟过长、则在 SER 引脚输入移位期间数据不会翻转、可能会导致 device2中的数据丢失。

我想知道、我是否应该在 device2 CLK 引脚中添加一些电容、以便在 device1 CLK 和 device2 CLK 之间添加一些延迟、从而确保器件2 SER 引脚中已设置数据信号、以避免丢失数据位?

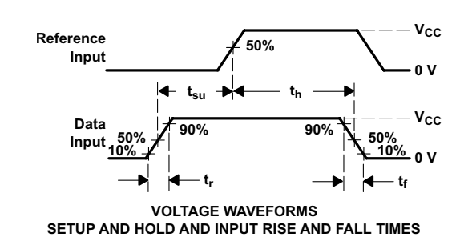

顺便说一下、我还想知道第三个波形的含义是什么? 这是否意味着输入信号应在 CLK 边沿信号之前就绪(完成设置)?

基准输入意味着什么?