请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74HC165 你(们)好

SN74HC165PWT 的 QH 引脚将从高电平跳到低电平(通常为高电平)。

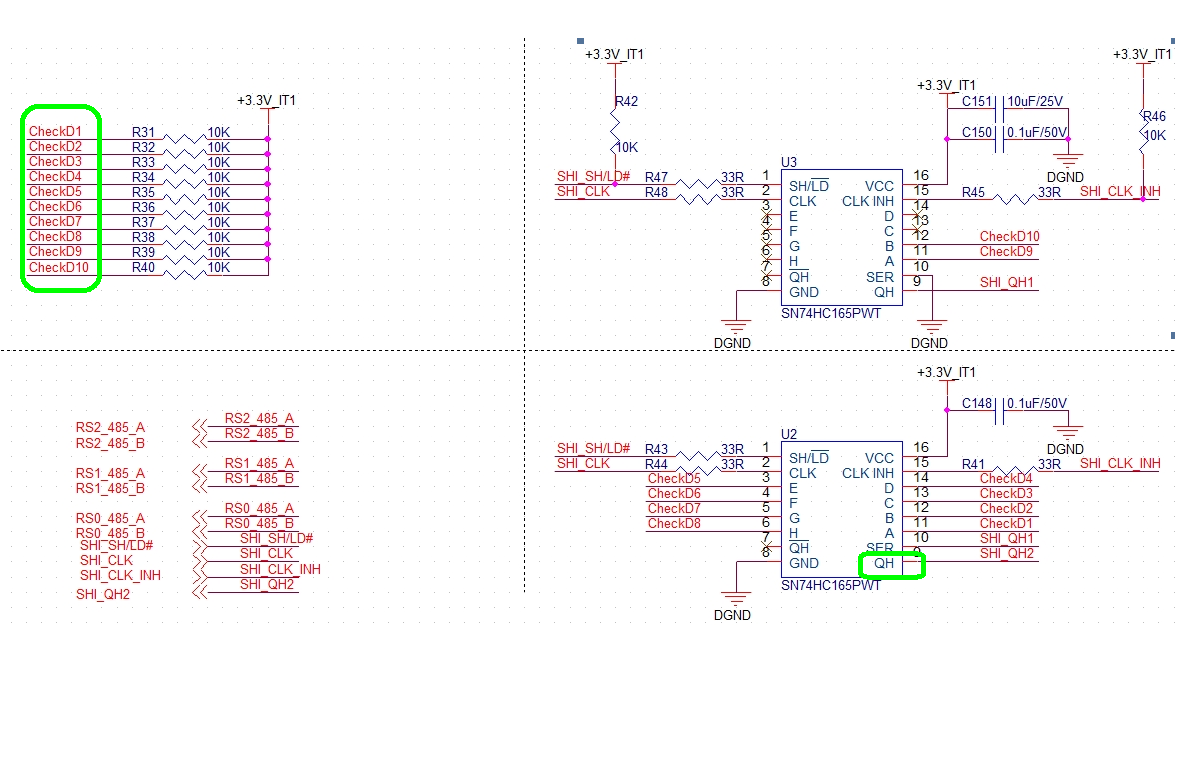

当 SN74HC165并行端口的输入正常工作时、它是10K 电阻上拉电阻(CheckD1~D10)。

在检测过程中、通过热插拔和接地这些并行端口是否存在损坏芯片的风险?

或者有其他可能的原因导致 QH 电压异常。

默认情况下、当 CheckD1-CheckD10的所有引脚被上拉时(没有引脚被拉至 DGND)、SHI_QH2的输出应该一直输出高电平;

当机器异常(U2异常)的输出时、SHI_QH2为低电平;下图是 FPGA 端子捕获的波形。

此致、

Jerry