Other Parts Discussed in Thread: SN74HCT74, SN54HCT74

主题中讨论的其他器件: SN54HCT74

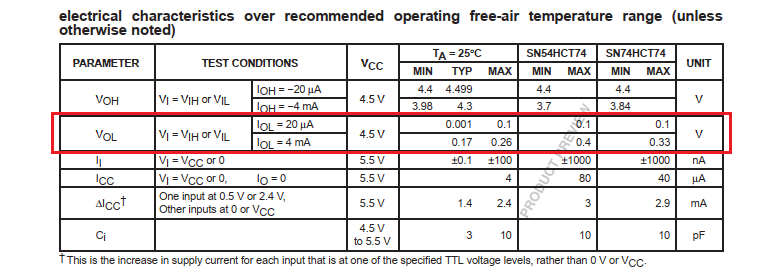

在 SN74HCT74的数据表中、第4页显示了"在推荐的自然通风工作温度范围内"的表格。 有三列、包括"Ta = 25°C"、"SN54HCT74"和"SN74HCT74"。

我知道、每个"SNxxxxxxx"列都显示了整个温度范围(-55 ~ 125°C 和-40 ~ 85°C)的最大开关时间、"TA"给出了室温(25°C)的典型和最大值、 但是、是否有图显示温度变化如何改变开关时间? 或者至少有一些基本的东西、比如开关时间会随着热量的增加或减少?

这是我要查看的数据表: http://www.ti.com/lit/ds/symlink/sn74hct74.pdf

谢谢、

Mike