主题中讨论的其他器件:SN74LV244A

您好、支持团队

我们在 SN74LVCH244APWR 中遇到了 CLK 和 LD 信号耦合问题。

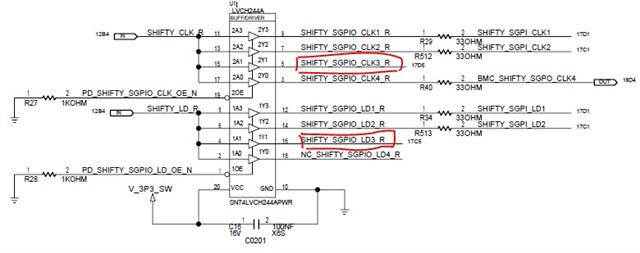

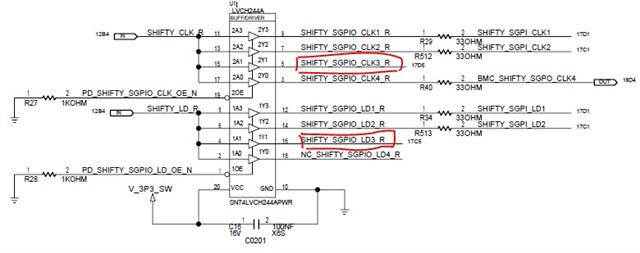

原理图:

问题:

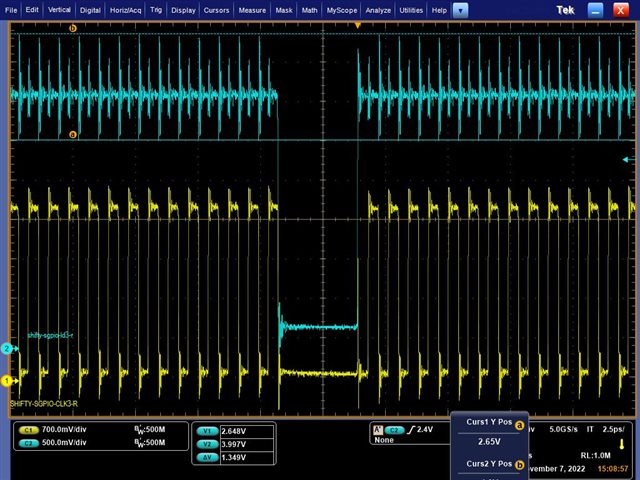

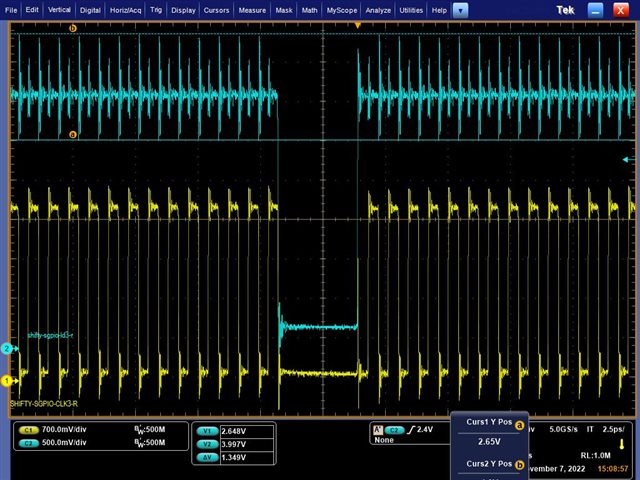

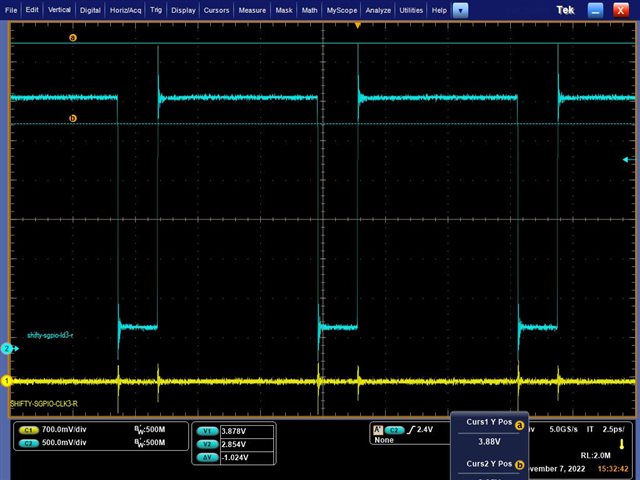

Shify_SGPIO_CLK_R 和 *** 具有以下图表中的耦合:

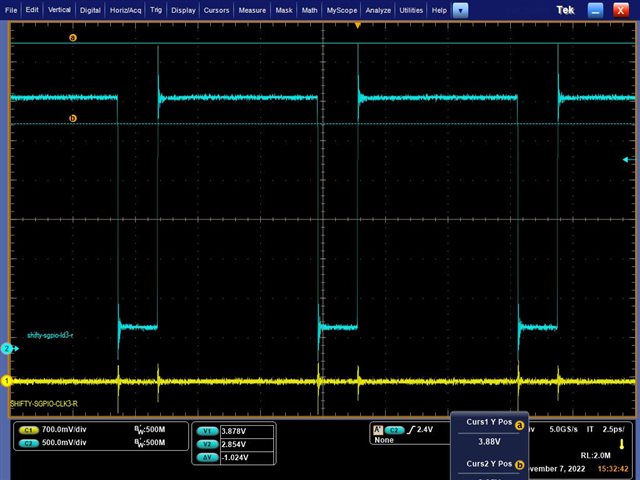

当我们从 SHIFT_CLK_R 中切断信号时、我们可以在 Shify_SGPIO_CLK_R 上看到耦合信号

如有任何建议、请告知我。

谢谢、

此致、

劳伦斯

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

您好、支持团队

我们在 SN74LVCH244APWR 中遇到了 CLK 和 LD 信号耦合问题。

原理图:

问题:

Shify_SGPIO_CLK_R 和 *** 具有以下图表中的耦合:

当我们从 SHIFT_CLK_R 中切断信号时、我们可以在 Shify_SGPIO_CLK_R 上看到耦合信号

如有任何建议、请告知我。

谢谢、

此致、

劳伦斯