Other Parts Discussed in Thread: LM567C, LMC567

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:LM567C 主题中讨论的其他器件: LMC567

您好!

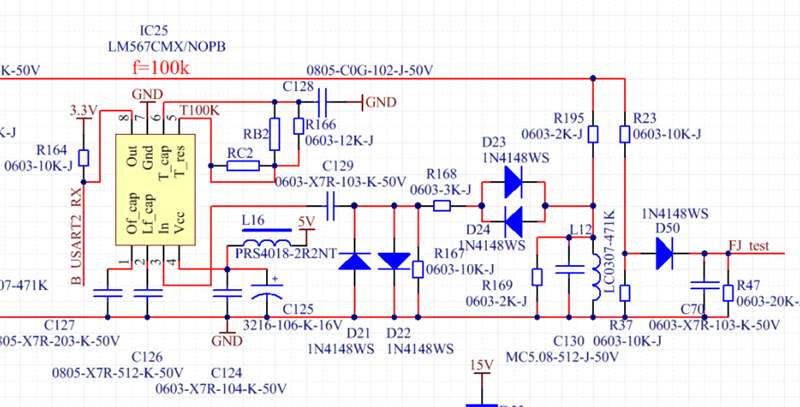

我将 LM567C 用作应用中的音频解码 器。原理图如下、中心频率设置为100KHz、带宽为14%。输入为700mV 100KHz 正弦信号。 问题是输入信号和 输出之间的延时时间可能很长。 在大多数情况下、器件输出在输入信号稳定后20us-100us 进入低电平状态、但有时延时可能会更长300us。

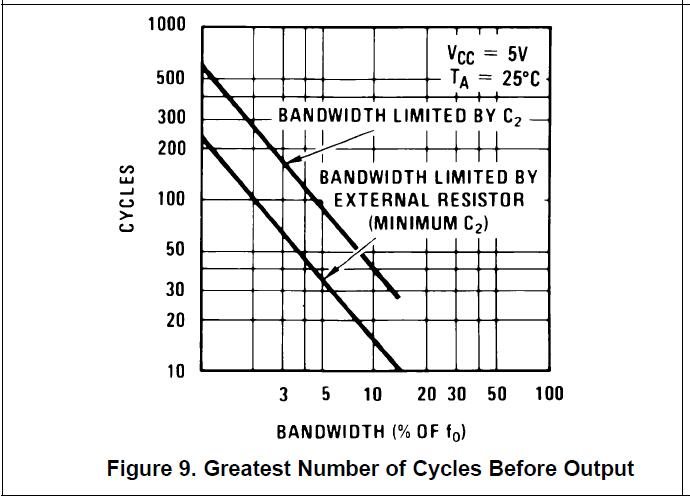

另一个问题:数据表中有聊天(图9)。 输出前的最大周期数)显示了输出前的带宽和周期之间的关系。 图中的一个是受外部电阻器(最小 C2)限制的带宽。 但我不了解外部电阻器带宽受限的情况。

如果输入和输出之间的延时时间将与 LMC567短路?

谢谢你。