请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LV595A 大家好、

我们将使用3个 SN74LV595A、如下面的原理图(最后一张图片)所示、并将这三个 QH'串联到下一级 SER。

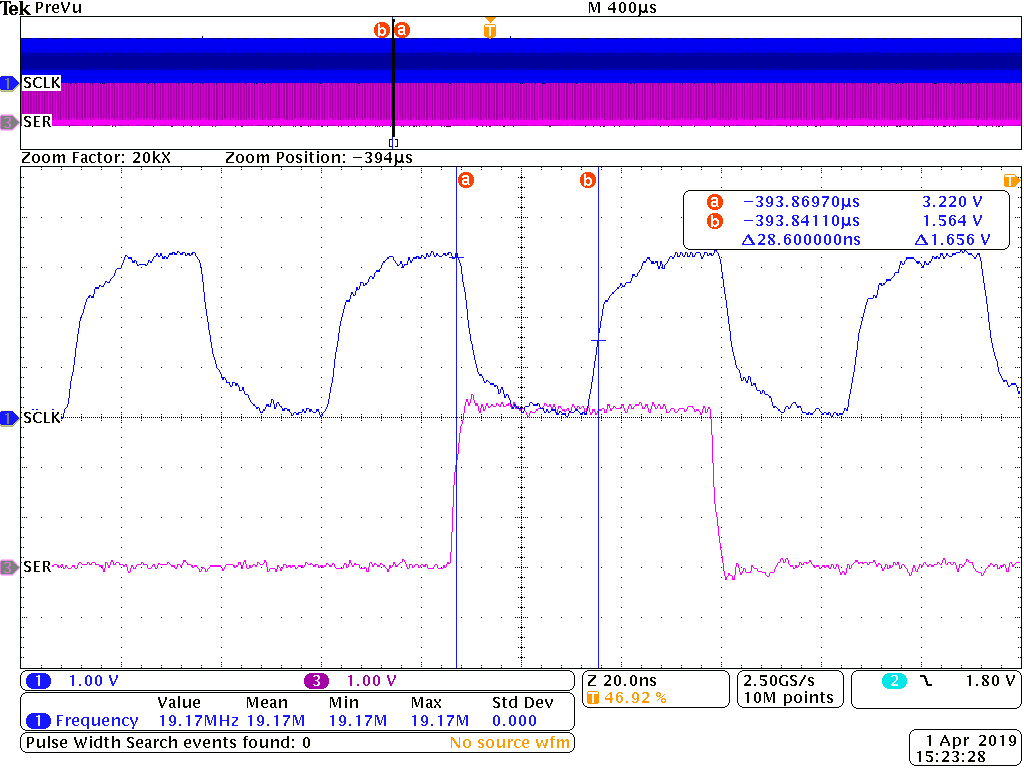

您可以在下图中看到、第一个和第三个部分对于 作为第二个图片波形的 SRCLK 上升规格之前的 SER 而言不是问题。 而第二部分 将在 SRCLK 上升规格问题之前具有 SER、因为它的半时钟周期更早、波形如第三幅图所示。

您对 SN74LV595A 系列或任何解决方案有什么了解吗?

或者只需关注第一级时序规格、而不关注第二部分时间?

谢谢!