Other Parts Discussed in Thread: SN74LVC1G125

请注意,本文内容源自机器翻译,可能存在语法或其它翻译错误,仅供参考。如需获取准确内容,请参阅链接中的英语原文或自行翻译。

器件型号:SN74LVC1G125 大家好

在查看 SN74LVC1G125数据表时、我在第10.2.1节中遇到了注释(复制如下)。

您能详细说明其含义吗?

您能否提供功能方框图和输出级架构的详细说明?

感谢您提供反馈

Ueli

----------------------------

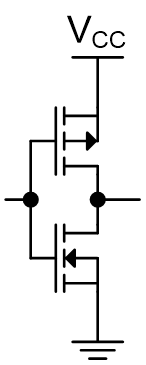

10.2.1设计要求此器件使用 CMOS 技术并具有平衡输出驱动。 应注意避免总线争用、因为它会驱动超过最大限制的电流。 高驱动也会在轻负载条件下产生快速边缘、因此应考虑布线和负载条件以防止振铃。