您好!

我们遇到了几种通过 VCCA 的电流消耗为1mA 至2mA 的情况。

大约5%的电路板(10万个电路板中)上会出现这种情况。

芯片已标记:WE245 87K G4 DDJE

其他信息:

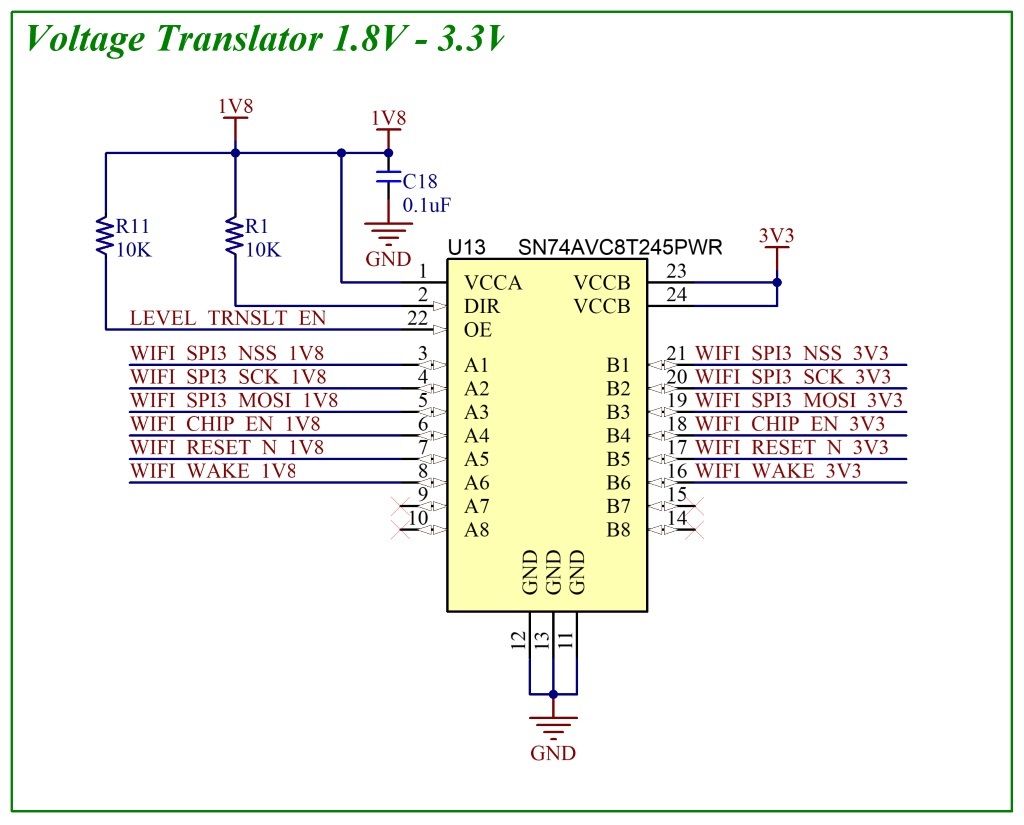

- 电流是在 VCCA 引脚上测得的。

- 已验证 OE 和 DIR 是否已上拉、所有端口 A 引脚均为输入、MCU 侧无上拉。 端口 B 和 VCCB 关闭。

- 与良好的芯片相比、保护二极管的值是可以的。

- 已尝试设置和复位端口 A 引脚(而不是将它们设置为输入)、电流消耗降至0.6mA。

- 已尝试将芯片移至良好的电路板、1mA 问题移至新电路板。

- 在故障电路板上组装良好的芯片、解决了故障电路板上的1mA 问题。

我们不确定导致此泄漏的原因、并想知道可以检查其他哪些方面以及我们可以采取哪些措施来纠正此问题。

谢谢、

吉尔