https://e2e.ti.com/support/logic-group/logic/f/logic-forum/868473/txs0104e-txs0104e-status-confirm

器件型号:TXS0104E尊敬的 TI:

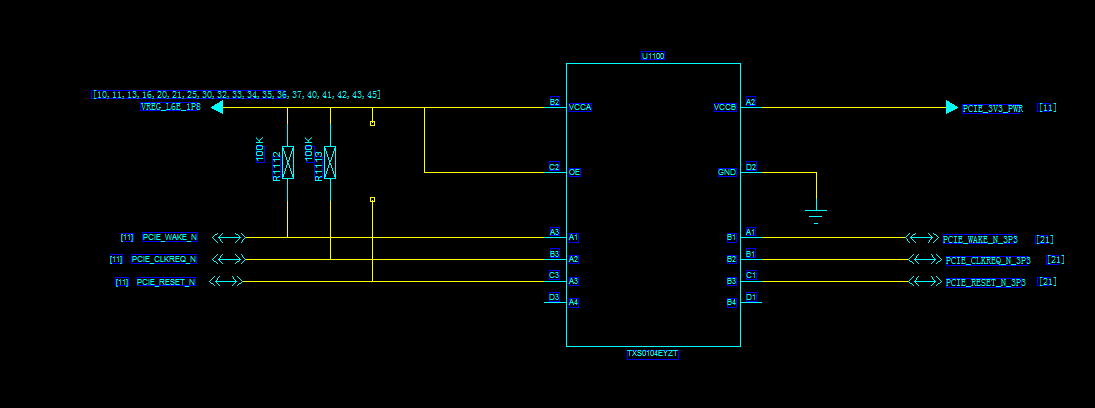

请帮助查看以下原理图、暂停我们要将信号从 PCIe_reset_N_3P3传输到 PCIe_reset_N、并由控制器接收、当 PCIe_reset_N_3P3为高电平时、控制器接收到高电平信号、当 PCIe_reset_N_3P3为低电平时、控制器接收到低电平信号、 但是、如果我们 暂停 PCIe_reset_N_3P3、 控制器也接收 到高电平信号、我认为这是异常状态。

那么、您能否给我们一些建议、当 PCIe_reset_N_3P3挂起时、控制器可以接收低电平信号。 (我们尝试使用下拉电阻、但它不起作用。)

谢谢你。

暂停