您好!

我对4层微控制器板的布局有疑问。 该板包含一个100MHz 微控制器、几个 Sigma-Delta-AD 转换器(16位、16SPS)和一些小尺寸逻辑器件。 我认为后者会在电路板上产生最高频率(信号时钟速度为低频率、例如100kHz、但 LVC 器件的边沿速度在5ns 范围内)。 因此、我不会将布局称为"要求"的"高速"布局。

我正在寻找 放置去 耦电容器的最佳做法、并被显然相互矛盾的准则所迷惑。

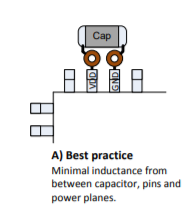

例如 ,http://www.ti.com/lit/an/spma056/spma056.pdf 的《TivaC 系列微控制器 TM4C129x 系列的系统设计指南》建议将此布局 布线选项作为最佳做法,位于第20页:

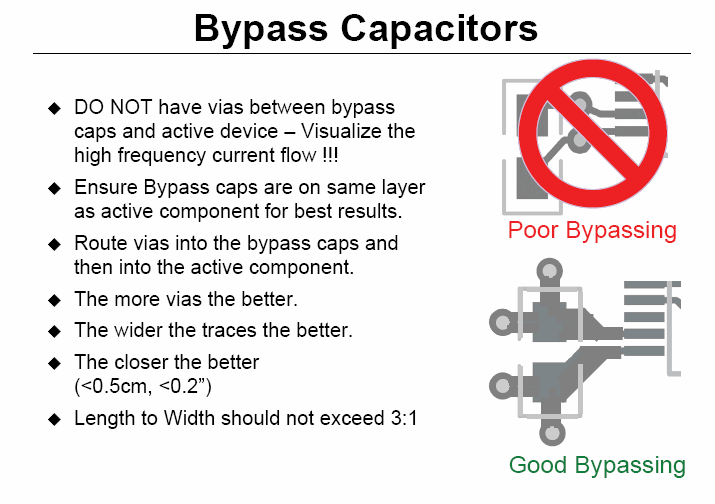

但是、以下 有关"高速设计"的 TI PowerPoint www.ti.com/.../slyp173.pdf 似乎完全拒绝了第5-23页上的"最佳实践":

我知道去耦电容器的问题可以讨论、也就是说、通过查看 TI 外部的来源、可以找到更不同的建议、例如 http://www.sigcon.com/Pubs/news/9_07.htm

我知道、当涉及高速设计(>1GHz)时、必须对单个布局应用仿真、才能"正确行事"、 但是、在低速设计(< 100MHz)领域、我希望至少在 TI 领域就"最佳实践"达成共识。 情况似乎并非如此。

我有点困惑。 请提供建议。 谢谢。