主题中讨论的其他器件: SN74AXC4T774

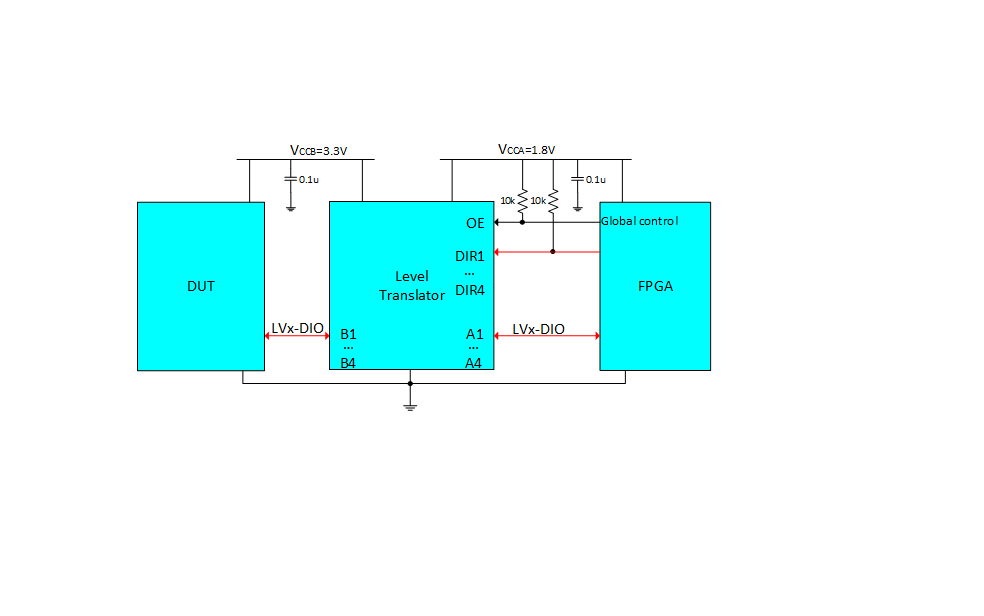

请参阅上面的原理图。 SN74AVC4T774用于从1.8V 到3.3V 的电压转换。

此设计建议的要求:

带宽:>50MHz,因此>100Mbps。

2. 1.8V 的设置与 FPGA 支持电压相同。 但 VccB 应该能够在1.2V 至3.3V 范围内针对 I/O 标准进行配置。

3.双向:独立 通道方向控制。

接口:由于 DUT 未知、因此数据链中需要三态。 因此、可通过 DUT 为 PU 或 PD 配置它。 电平转换器中不允许使用 PU/PD 电阻器。

SN74AVC4T774可用于高速>100Mbps、1.2V-3.3V 电压范围、独立 DIR 控制引脚。 加电/断电完成前、只有一个 OE 引脚可用于高阻态设置为高电平。

要求1和2是可以的、但3和4中有一些问题:

3:我的设计需要在数据传输期间读回信息。 因此、在运行期间将改变方向。

在 TI 的一些 数据表中、使用 DIR 控制引脚的电平转换器。 首先禁用器件所需的器件、然后再次启用器件后设置 DIR。 是否需要启用和禁用 SN74AVC4T77? 能否在正常运行期间将 OE 设为低电平、然后在运行期间无限制地将 DIR 设为双向功能?

4.我在论坛上看到了一些讨论、意见一直是积极的。 因此、SN74AVC4T774需要 PU/PD。 这是否用于低功耗?

但对于我的设计、正如我们之前所说的。 逻辑电平应由未知 DUT 设置。 它可以是高电平或低电平。 我们无法在电平转换器上生成 PD/PU。

最坏的情况是:从 DUT 到 FPGA (B-A)的方向、DUT 没有信号可能悬空(软件可能会 将其设置为空闲状态下的低电平)、SN74AVC4T774上没有 PD/PU。 这会是一个大问题吗?

此致

荣鹏扎海