大家好、TI 论坛、

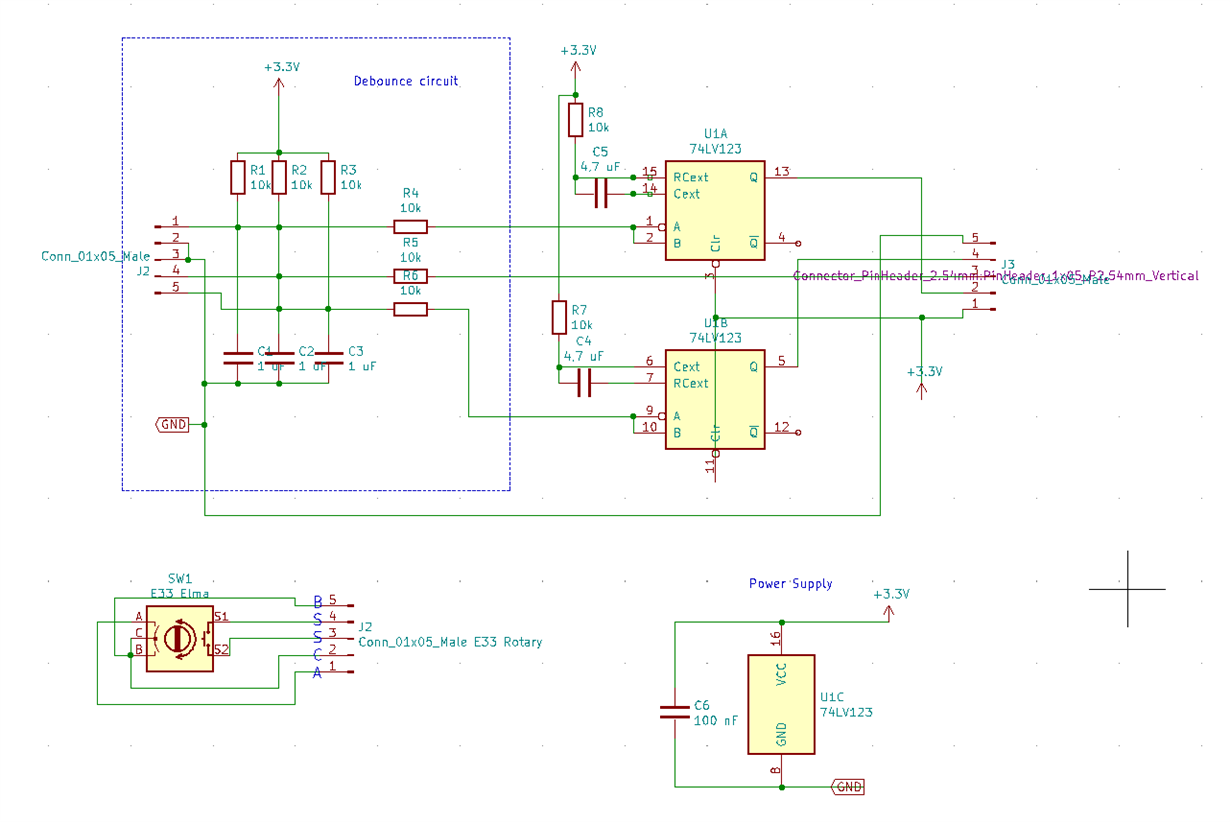

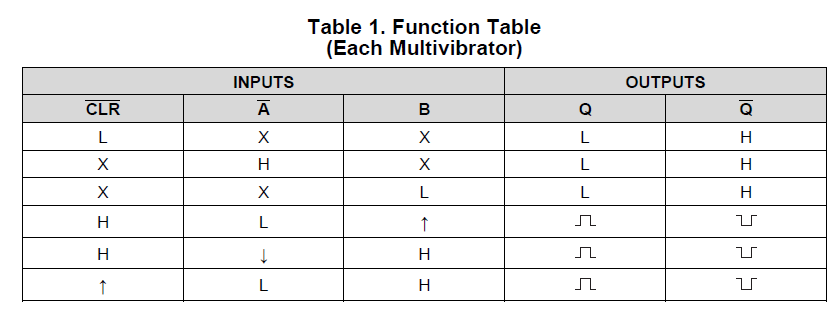

我尝试在同一信号的上升沿和下降沿触发 SN74LV123A。

为此、我短接了同一信道的两个输入(inv.non-inv)。

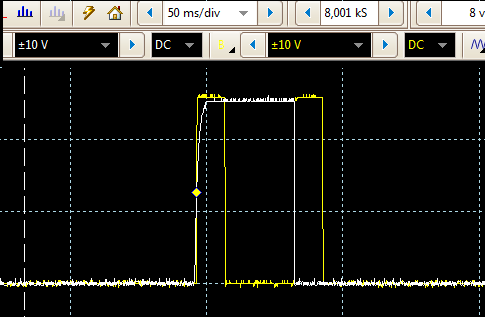

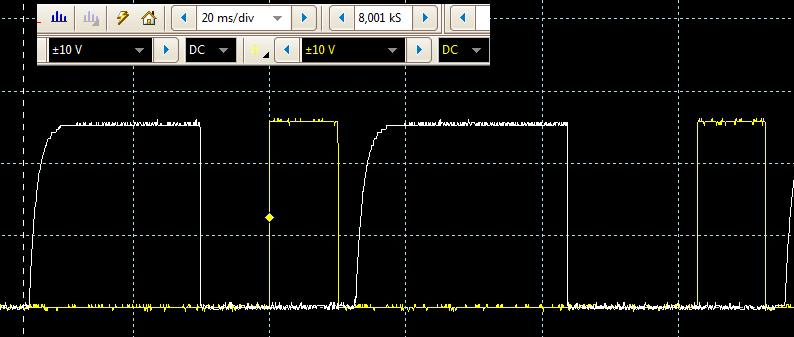

I 在 CHA (P1&P2的白色输入)上工作正常、黄色=输出 P13)

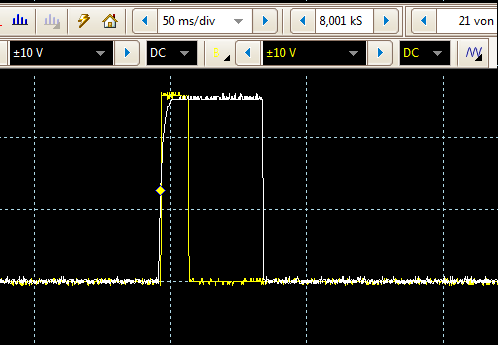

至于通道 B、它在下降沿( P9&P10的白色输入)上触发n´t μ s、黄色=输出 P5)

我是否遗漏了什么?

我´s 换用组件、信号源(双通道旋转编码器)、不同的 IC Δ Σ 等、但什么也不起作用。

是否可以将 IC 设计为在该模式下工作? 为什么它适用于通道 A、而不适用于通道 B?

´s 考虑在两个 IC 上使用通道 A、但应浪费 PCB 空间等。

我希望有人能帮忙:)

电路如下: